dzielnik częstotliwości - Frequency divider

Dzielnik częstotliwości , nazywane również dzielnik zegara lub przelicznik lub z offsetem , to obwód , który pobiera sygnał wejściowy o częstotliwości , i generuje sygnał wyjściowy o częstotliwości:

gdzie jest liczbą całkowitą. Pętla synchronizacji fazowej syntezatory częstotliwości, korzystają dzielniki częstotliwości do generowania częstotliwości, która jest wielokrotnością częstotliwości odniesienia. Dzielnik częstotliwości może być realizowany zarówno analogowych i cyfrowych zastosowań.

Zawartość

dzielniki analogowe

Analogowych dzielników częstotliwości są mniej częste i stosować tylko przy bardzo wysokich częstotliwościach. dzielniki cyfrowe realizowane w nowoczesnych technologiach IC może pracować aż do kilkudziesięciu GHz.

Rotacyjny dzielnik częstotliwości

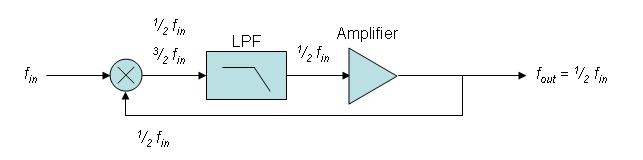

Regeneracyjny dzielnik częstotliwości, znany również jako Miller dzielnika częstotliwości , miksuje sygnał wejściowy z sygnałem sprzężenia zwrotnego z mieszalnika.

Sygnał sprzężenia zwrotnego . To daje sumę i różnicę częstotliwości , na wyjściu miksera. Filtr dolnoprzepustowy usuwa wyższej częstotliwości i częstotliwość jest wzmacniany i doprowadzany z powrotem do mieszalnika.

Wtrysk zablokowana częstotliwość dzielnik

Sypki oscylator , który ma małą wysokość sygnału o wyższej częstotliwości doprowadza się będzie miał tendencję do drgań w fazie z sygnałem wejściowym. Takie dzielnik częstotliwości były niezbędne w rozwoju telewizji .

To działa podobnie do oscylatora wtrysku zablokowane . W iniekcji zamknięty dzielnik częstotliwości, częstotliwości sygnału wejściowego jest wielokrotnością (lub frakcji) o wolnym biegu częstotliwości oscylatora. Chociaż te dzielnik częstotliwości są na ogół niższe niż moc statyczne szerokopasmowego (klapek oparciu) dzielnik częstotliwości, wadą jest ich niski zakres blokujących. Zakres blokujący ILFD jest odwrotnie proporcjonalna do współczynnika jakości (Q) w zbiorniku oscylatora. W zintegrowanych wzorów obwodów, to sprawia, że ILFD wrażliwy na przetwarzanie odmiany. Należy dołożyć starań, aby zapewnić zakres przestrajania obwodu napędowego (na przykład generator sterowany napięciem) musi mieścić się w zakresie blokowania wprowadzania w ILFD.

cyfrowe dzielniki

W przypadku zasilania z-2 podział całkowitej, prosty licznik binarny może być używany, taktowany przez sygnał wejściowy. Najmniej znaczący bit wyjściowy naprzemiennie na 1/2 stopy zegara wejściowego, następny bit przy 1/4 prędkości, trzeci bit na 1/8 stopy, itp układ flipflops jest klasyczną metodą całkowitej -n podział. Taki podział jest częstotliwość i faza spójne źródła na różne środowiska, w tym temperatury. Najprostszym konfiguracji, gdzie każdy cykl przerzutnik jest dzielenie przez 2. Dla serii trzech z nich, system taki byłby dzielenie przez 8. Przez dodanie kolejnych bramek logicznych z łańcuchem klapki inne współczynniki podziału mogą być uzyskane. Zintegrowane rodziny obwód logiczny może stanowić jedno rozwiązanie wióra dla niektórych typowych proporcjach podziału.

Innym popularnym obwód podzielić sygnał cyfrowy przez wielu nawet całkowitej jest licznik Johnsona . Jest to rodzaj rejestru przesuwnego sieci, który jest taktowany sygnałem wejściowym. Uzupełnieniem wyjście Ostatni rejestr jest zawracany do wejścia pierwszego rejestru jest. Sygnał wyjściowy pochodzi z co najmniej jednego z wyjść rejestru. Na przykład, rozdzielacz dzielenie przez 6 może być wykonana z blatem 3 zarejestrować Johnsona. Sześć ważne wartości Licznika 000, 100, 110, 111, 011 i 001. Ten wzór powtarza się za każdym razem, gdy sieć jest taktowany przez sygnał wejściowy. Wyjście każdego rejestru jest AF / 6 o przebiegu prostokątnym z 60 ° przesunięcia fazowego pomiędzy rejestry. Rejestry dodatkowe mogą być dodawane w celu dostarczenia dodatkowych dzielników całkowitych.

Mieszane podział sygnału

( Klasyfikacja: asynchroniczny sekwencyjnego logiczny )

Układ D przerzutników są klasyczne metody całkowitą N podziału. Taki podział jest częstotliwość i faza spójne źródła na różne środowiska, w tym temperatury. Najprostszym konfiguracji, gdzie każdy cykl przerzutnik D jest dzielenie przez 2. Dla serii trzech z nich, system taki byłby dzielenie przez 8. Bardziej skomplikowane konfiguracje stwierdzono generujących nieparzyste czynników, takich jak dzielenie przez 5. Standard, klasyczne chipy logiczne, które realizują ten lub podobne funkcje podziałem częstotliwości obejmują 7456, 7457, 74292, 74294. a (patrz Lista serii 7400 układów scalonych )

Cząstkowej N przekładki

Ułamkowa N syntezator częstotliwości może być skonstruowana za pomocą dwóch przegród liczbą całkowitą, a N dzielenia przez i dzielenia kroku (n + 1) dzielnika częstotliwości. Z kontrolerem modułu n jest przełączana pomiędzy tymi dwoma wartościami, tak że VCO naprzemiennie jednym zablokowanym częstotliwości i drugiej. VCO stabilizuje się z częstotliwością, która jest średni czas dwóch zablokowanych częstotliwości. Zmieniając procent czasu dzielnik częstotliwości spędza na dwóch wartości dzielnika, częstotliwość VCO zablokowanej można wybierać z bardzo drobnej ziarnistości.

Delta-sigma cząstkowej N syntezatory

Jeśli sekwencją dzielenia przez N i podzielić przez (n + 1) jest okresowe sygnały zakłócające pojawiają się na wyjściu VCO oprócz pożądanej częstotliwości. Delta-sigma cząstkowej N przekładki przezwyciężyć ten problem przez bezładność wybór n i (n + 1), przy utrzymaniu proporcji czasu uśrednionego.

Zobacz też

Referencje

- ^ RL Miller (1939). „Cząstkowe generatorów częstotliwości Wykorzystując Rotacyjny modulacja”. Proceedings of the IRE . 27 (7): 446-457. doi : 10,1109 / JRPROC.1939.228513 .