Intel 8085 - Intel 8085

Wariant procesora Intel P8085AH-2 z czarnymi plastikowymi i srebrnymi pinami

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | Marzec 1976 |

| Wycofane | 2000 |

| Wspólni producenci | |

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | 3, 5 i 6 MHz |

| Szerokość danych | 8 bitów |

| Szerokość adresu | 16 bitów |

| Architektura i klasyfikacja | |

| Min. rozmiar funkcji | 3 µm |

| Zestaw instrukcji | 8085 |

| Specyfikacje fizyczne | |

| Tranzystory | |

| Pakiet(y) | |

| Gniazdo(a) | |

| Historia | |

| Poprzednik | Intel 8080 |

| Następca | Intel 8086 |

Intel 8085 ( „ osiemdziesiąt osiemdziesiąt pięć lat ”) jest 8-bitowy mikroprocesor produkowany przez firmę Intel i wprowadzony w marcu 1976. Jest oprogramowaniem binarnie kompatybilny z bardziej znanego Intel 8080 tylko z dwoma instrukcjami drobnych dodawanych do wspierania jego dodano funkcje przerwań i wejścia/wyjścia szeregowego. Wymaga jednak mniej obwodów pomocniczych, co pozwala na budowanie prostszych i tańszych systemów mikrokomputerowych .

Cyfra „5” w liczbie części podkreślono, że 8085 wykorzystuje pojedynczy 5- + V (V), za pomocą zasilacza wyczerpywanie trybu tranzystorów zamiast konieczności +5 V -5 V do +12 V materiałów potrzebnych przez 8080. Możliwości te odpowiadały możliwościom konkurencyjnego Z80 , popularnego procesora wywodzącego się z 8080 wprowadzonego rok wcześniej. Procesory te mogą być używane w komputerach z systemem operacyjnym CP/M .

8085 jest dostarczany w 40-pinowej obudowie DIP . Aby zmaksymalizować funkcje na dostępnych pinach, 8085 używa multipleksowanej magistrali adresu/danych (AD^0-AD^7). Jednak obwód 8085 wymaga 8-bitowego zatrzasku adresu, więc Intel wyprodukował kilka układów wspierających z wbudowanym zatrzaskiem adresu. Należą do nich 8755 z zatrzaskiem adresu, 2 KB pamięci EPROM i 16 pinami we/wy oraz 8155 z 256 bajtami pamięci RAM, 22 pinami I/O i 14-bitowym programowalnym timerem/licznikiem. Zmultipleksowana magistrala adresowa/danych zmniejszyła liczbę ścieżek PCB między 8085 a takimi układami pamięci i I/O.

Zarówno 8080, jak i 8085 zostały przyćmione przez Zilog Z80 dla komputerów stacjonarnych, który przejął większość rynku komputerów CP/M, a także udział w dynamicznie rozwijającym się rynku komputerów domowych na początku i w połowie lat 80. XX wieku.

8085 miał długą żywotność jako kontroler, bez wątpienia dzięki wbudowanemu szeregowemu we/wy i pięciu priorytetowym przerwaniom, prawdopodobnie cechom podobnym do mikrokontrolera, których nie miał procesor Z80. Kiedyś zaprojektowany do takich produktów, jak kontroler DECtape II i terminal wideo VT102 pod koniec lat 70., 8085 służył do nowej produkcji przez cały okres życia tych produktów. Okres ten był zwykle dłuższy niż żywotność komputerów stacjonarnych.

Opis

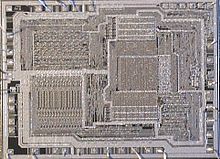

8085 to konwencjonalna konstrukcja von Neumanna oparta na procesorze Intel 8080. W przeciwieństwie do 8080 nie multipleksuje sygnałów stanu do magistrali danych, ale zamiast tego 8-bitowa magistrala danych jest multipleksowana z niższymi ośmioma bitami 16-bitowej magistrali adresowej aby ograniczyć liczbę pinów do 40. Sygnały stanu są dostarczane przez dedykowane piny sygnału sterującego magistralą i dwa dedykowane piny identyfikujące stan magistrali o nazwach S0 i S1. Pin 40 jest używany do zasilania (+5 V), a pin 20 do masy. Pin 39 jest używany jako pin Hold. Procesor został zaprojektowany przy użyciu obwodów nMOS , a późniejsze wersje „H” zostały zaimplementowane w ulepszonym procesie nMOS firmy Intel zwanym HMOS („High-performance MOS”), pierwotnie opracowanym dla szybkich statycznych produktów RAM. Potrzebny jest tylko jeden zasilacz 5 V, podobnie jak konkurencyjne procesory i w przeciwieństwie do 8080. 8085 wykorzystuje około 6500 tranzystorów .

8085 zawiera funkcje 8224 (generator zegara) i 8228 (kontroler systemu) na chipie, zwiększając poziom integracji. Minusem w porównaniu do podobnych współczesnych projektów (takich jak Z80) jest fakt, że autobusy wymagają demultipleksowania; Jednak zatrzaski adresowe w układach pamięci Intel 8155, 8355 i 8755 umożliwiają bezpośredni interfejs, więc 8085 wraz z tymi układami stanowi prawie kompletny system.

8085 posiada rozszerzenia do obsługi nowych przerwań, z trzema maskowalnymi przerwaniami wektorowymi (RST 7.5, RST 6.5 i RST 5.5), jednym niemaskowalnym przerwaniem (TRAP) i jednym zewnętrznie obsługiwanym przerwaniem (INTR). Każde z tych pięciu przerwań ma osobny pin na procesorze, co pozwala prostym systemom uniknąć kosztu oddzielnego kontrolera przerwań. Przerwanie RST 7.5 jest wyzwalane zboczem (zatrzaskiwane), podczas gdy RST 5.5 i 6.5 są wrażliwe na poziom. Wszystkie przerwania są włączane przez instrukcję EI i wyłączane przez instrukcję DI. Dodatkowo, instrukcje SIM (Set Interrupt Mask) i RIM (Read Interrupt Mask), jedyne instrukcje 8085, które nie pochodzą z 8080, pozwalają na indywidualne maskowanie każdego z trzech maskowalnych przerwań RST. Wszystkie trzy są maskowane po normalnym resecie procesora. SIM i RIM umożliwiają również odczytanie stanu globalnej maski przerwań i trzech niezależnych stanów maski przerwań RST, odczytanie stanów oczekujących tych samych trzech przerwań, zresetowanie przerzutnika wyzwalacza RST 7.5 (anulowanie oczekujące przerwanie bez jego obsługi) oraz dane szeregowe do wysłania i odebrania odpowiednio przez piny SOD i SID, wszystko pod kontrolą programu i niezależnie od siebie.

Karty SIM i RIM są wykonywane w czterech cyklach zegara (stany T), dzięki czemu możliwe jest próbkowanie SID i/lub przełączanie SOD znacznie szybciej niż możliwe jest przełączanie lub próbkowanie sygnału za pośrednictwem dowolnego portu we/wy lub portu mapowanego w pamięci, np. jednego portu 8155. (W ten sposób SID można porównać do pinu SO ["Ustaw przepełnienie"] procesora 6502 współczesnego do 8085.)

Podobnie jak 8080, 8085 może pomieścić wolniejsze pamięci poprzez zewnętrznie generowane stany oczekiwania (pin 35, READY) i ma możliwość bezpośredniego dostępu do pamięci (DMA) przy użyciu sygnałów HOLD i HLDA (piny 39 i 38). Ulepszenie w stosunku do 8080 polega na tym, że 8085 może sam sterować kryształem piezoelektrycznym bezpośrednio z nim połączonym, a wbudowany generator zegara generuje wewnętrzne dwufazowe sygnały zegarowe o wysokiej amplitudzie przy połowie częstotliwości kryształu (kryształ 6,14 MHz dawałby na przykład zegar 3,07 MHz). Zegar wewnętrzny jest dostępny na styku wyjściowym, aby sterować urządzeniami peryferyjnymi lub innymi procesorami w synchronizacji krokowej z procesorem, z którego wyprowadzany jest sygnał. 8085 może być również taktowany przez zewnętrzny oscylator (dzięki czemu możliwe jest używanie 8085 w synchronicznych systemach wieloprocesorowych przy użyciu wspólnego zegara systemowego dla wszystkich procesorów lub do synchronizacji procesora z zewnętrznym czasem odniesienia, takim jak ten z źródło wideo lub precyzyjny czas odniesienia).

8085 jest kontynuacją zgodną z binarną wersją 8080. Obsługuje kompletny zestaw instrukcji 8080, z dokładnie tym samym zachowaniem instrukcji, w tym wszystkimi efektami na flagach procesora (z wyjątkiem operacji AND/ANI, która ustawia AC oznaczyć inaczej). Oznacza to, że zdecydowana większość kodu obiektowego (dowolny obraz programu w pamięci ROM lub RAM), który pomyślnie działa na 8080, może działać bezpośrednio na 8085 bez translacji lub modyfikacji. (Wyjątki obejmują kod krytyczny czasowo i kod, który jest wrażliwy na wspomnianą różnicę w ustawieniu flagi AC lub różnice w nieudokumentowanym zachowaniu procesora.) Czasy instrukcji 8085 różnią się nieznacznie od 8080 — niektóre operacje 8-bitowe, w tym INR, DCR i intensywnie używane instrukcje MOV r,r' są o jeden cykl zegara szybsze, ale instrukcje, które obejmują operacje 16-bitowe, w tym operacje na stosie (które zwiększają lub zmniejszają 16-bitowy rejestr SP) generalnie są o jeden cykl wolniejsze. Oczywiście możliwe jest, że rzeczywiste 8080 i/lub 8085 różnią się od opublikowanych specyfikacji, szczególnie w subtelnych szczegółach. (To samo nie dotyczy Z80.) Jak już wspomniano, tylko instrukcje SIM i RIM były nowe w 8085.

Model programowania

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Procesor ma siedem 8-bitowych rejestrów dostępnych dla programisty o nazwach A, B, C, D, E, H i L, gdzie A jest również znany jako akumulator. Pozostałe sześć rejestrów może być używanych jako niezależne rejestry bajtowe lub jako trzy 16-bitowe pary rejestrów, BC, DE i HL (lub B, D, H, jak określono w dokumentach Intel), w zależności od konkretnej instrukcji. Niektóre instrukcje używają HL jako (ograniczonego) 16-bitowego akumulatora. Podobnie jak w 8080, zawartość adresu pamięci wskazywanego przez HL może być dostępna jako pseudorejestr M. Ma również 16-bitowy licznik programu i 16-bitowy wskaźnik stosu do pamięci (zastępując wewnętrzny stos 8008 ). Instrukcje takie jak PUSH PSW, POP PSW wpływają na słowo statusu programu (akumulator i flagi). Akumulator przechowuje wyniki operacji arytmetycznych i logicznych, a bity rejestru flag (znak, zero, pomocnicze przeniesienie, parzystość i flagi przeniesienia) są ustawiane lub usuwane zgodnie z wynikami tych operacji. Flaga znaku jest ustawiana, jeśli wynik ma znak ujemny (tzn. jest ustawiana, jeśli ustawiony jest bit 7 akumulatora). Flaga pomocnicza lub połowa przeniesienia jest ustawiana, jeśli nastąpiło przeniesienie z bitu 3 na bit 4. Flaga parzystości jest ustawiona na 1, jeśli parzystość (liczba 1-bitów) akumulatora jest parzysta; jeśli jest to dziwne, jest wyczyszczone. Flaga zero jest ustawiana, jeśli wynik operacji wynosił 0. Na koniec flaga przeniesienia jest ustawiana, jeśli nastąpiło przeniesienie z bitu 7 akumulatora (MSB).

Polecenia/instrukcje

Jak w wielu innych 8-bitowych procesorach, wszystkie instrukcje są zakodowane w jednym bajcie (włącznie z numerami rejestrów, ale z wyłączeniem danych bezpośrednich), dla uproszczenia. Po niektórych z nich następuje jeden lub dwa bajty danych, które mogą być operandem bezpośrednim, adresem pamięci lub numerem portu. Instrukcja NOP "brak operacji" istnieje, ale nie modyfikuje żadnego z rejestrów ani flag. Podobnie jak większe procesory, zawiera instrukcje CALL i RET dla wielopoziomowych wywołań procedur i zwrotów (które mogą być wykonywane warunkowo, jak skoki) oraz instrukcje zapisywania i przywracania dowolnej 16-bitowej pary rejestrów na stosie maszyny. Istnieje również osiem jednobajtowych instrukcji wywołania (RST) dla podprogramów znajdujących się pod stałymi adresami 00h, 08h, 10h,...,38h. Są one przeznaczone do dostarczania przez zewnętrzny sprzęt w celu wywołania odpowiedniej procedury obsługi przerwań, ale są również często wykorzystywane jako szybkie wywołania systemowe. Jedną z zaawansowanych instrukcji jest XTHL, która służy do wymiany pary rejestrów HL na wartość przechowywaną pod adresem wskazanym przez wskaźnik stosu.

8-bitowe instrukcje

Wszystkie dwuargumentowe 8-bitowe operacje arytmetyczno-logiczne (ALU) działają na 8-bitowym akumulatorze (rejestr A). W przypadku operacji 8-bitowych z dwoma argumentami, drugi argument może być wartością natychmiastową, innym rejestrem 8-bitowym lub komórką pamięci adresowaną przez 16-bitową parę rejestrów HL. Jedyne 8-bitowe operacje ALU, które mogą mieć miejsce docelowe inne niż akumulator, to jednoargumentowe instrukcje inkrementacji lub dekrementacji, które mogą działać na dowolnym 8-bitowym rejestrze lub w pamięci adresowanej przez HL, tak jak w przypadku dwuargumentowych operacji 8-bitowych. Kopiowanie bezpośrednie jest obsługiwane między dowolnymi dwoma rejestrami 8-bitowymi oraz między dowolnym rejestrem 8-bitowym a komórką pamięci o adresie HL, przy użyciu instrukcji MOV. Wartość natychmiastową można również przenieść do dowolnego z powyższych miejsc docelowych za pomocą instrukcji MVI. Ze względu na regularne kodowanie instrukcji MOV (wykorzystujące prawie jedną czwartą całej przestrzeni opcode) istnieją nadmiarowe kody do kopiowania rejestru do samego siebie ( na przykład MOV B,B ), które są mało przydatne, z wyjątkiem opóźnień. Jednak to, co byłoby kopią komórki zaadresowanej HL do siebie (tj. MOV M,M ) zamiast tego koduje instrukcję HLT , wstrzymując wykonywanie do momentu wystąpienia zewnętrznego resetu lub niezamaskowanego przerwania.

operacje 16-bitowe

Chociaż 8085 jest procesorem 8-bitowym, ma kilka operacji 16-bitowych. Każda z trzech 16-bitowych par rejestrów (BC, DE, HL lub SP) może być załadowana natychmiastową 16-bitową wartością (przy użyciu LXI), inkrementowana lub dekrementowana (przy użyciu INX i DCX) lub dodana do HL (przy użyciu DAD ). LHLD ładuje HL z bezpośrednio adresowanej pamięci, a SHLD również przechowuje HL. Operacja XCHG wymienia wartości HL i DE. Dodanie HL do samego siebie wykonuje 16-bitowe arytmetyczne przesunięcie w lewo za pomocą jednej instrukcji. Jedyną 16-bitową instrukcją, która wpływa na dowolną flagę, jest DAD (dodawanie BC, DE, HL lub SP do HL), która aktualizuje flagę przeniesienia w celu ułatwienia 24-bitowych lub większych dodawania i przesunięć w lewo. Dodanie wskaźnika stosu do HL jest przydatne do indeksowania zmiennych w (rekurencyjnych) ramkach stosu. Ramkę stosu można przydzielić za pomocą DAD SP i SPHL, a odgałęzienie do obliczonego wskaźnika można wykonać za pomocą PCHL. Te możliwości umożliwiają kompilację języków takich jak PL/M , Pascal lub C z 16-bitowymi zmiennymi i tworzenie kodu maszynowego 8085. Odejmowanie i bitowe operacje logiczne na 16 bitach są wykonywane w 8-bitowych krokach. Operacje, które muszą być zaimplementowane przez kod programu (biblioteki podprogramów) obejmują porównywanie liczb całkowitych ze znakiem oraz mnożenie i dzielenie.

Nieudokumentowane instrukcje

Szereg nieudokumentowanych instrukcji i flag zostało odkrytych przez dwóch inżynierów oprogramowania, Wolfganga Dehnhardta i Villy'ego M. Sorensena w trakcie opracowywania asemblera 8085. Instrukcje te wykorzystują 16-bitowe operandy i obejmują pośrednie ładowanie i przechowywanie słowa, odejmowanie, przesunięcie, obracanie i operacje przesunięcia.

Schemat wejścia/wyjścia

8085 obsługuje do 256 portów wejścia/wyjścia (I/O), dostępnych za pomocą dedykowanych instrukcji wejścia/wyjścia — biorąc adresy portów jako operandy. Ten schemat mapowania I/O jest uważany za zaletę, ponieważ uwalnia ograniczoną przestrzeń adresową procesora. Instrukcje IN i OUT służą do odczytu i zapisu danych portu we/wy. W cyklu magistrali I/O 8-bitowy adres I/O jest wyprowadzany przez CPU zarówno w dolnej, jak i górnej połówce 16-bitowej magistrali adresowej.

Dostęp do mapowanych w pamięci urządzeń we/wy można również uzyskać za pomocą instrukcji LDA (ładuj akumulator z 16-bitowego adresu) i STA (zapisz akumulator pod określonym adresem 16-bitowym) lub dowolnych innych instrukcji, które mają operandy pamięci.

System rozwoju

Firma Intel wyprodukowała serię systemów rozwojowych dla 8080 i 8085, znanych jako system mikroprocesorowy MDS-80. Oryginalny system rozwojowy miał procesor 8080. Później dodano obsługę 8085 i 8086, w tym ICE ( emulatory w obwodzie ). Jest to duże i ciężkie pudełko typu desktop, około 20-calowej kostki (w kolorze korporacyjnym firmy Intel), w którym znajduje się procesor, monitor i pojedyncza 8-calowa stacja dyskietek. Później udostępniono zewnętrzne pudełko z dwoma kolejnymi dyskietkami. dyski. To prowadzi ISIS systemu operacyjnego i może również stosować emulator kapsułę i zewnętrznego EPROM programista. To urządzenie wykorzystuje gniazdo karty Multibus który był przeznaczony tylko dla systemu rozwoju. zaskakująca liczba części klatki kart i procesorów były sprzedawane, co doprowadziło do rozwoju Multibusa jako osobnego produktu.

Późniejszy iPDS jest urządzeniem przenośnym o wymiarach około 8 x 16 x 20 cali z uchwytem. Ma mały zielony ekran, klawiaturę wbudowaną w górę, napęd dyskietek 5¼ cala i obsługuje ISIS-II. Może również przyjąć drugi procesor 8085, co pozwala na ograniczoną formę pracy wieloprocesorowej, w której oba procesory działają jednocześnie i niezależnie. Ekran i klawiaturę można przełączać między nimi, co pozwala na łączenie programów na jednym procesorze (duże programy chwilę) podczas gdy pliki są edytowane w drugim.Posiada opcję pamięci bąbelkowej i różne moduły programistyczne, w tym EPROM i moduły programistyczne Intel 8048 i 8051 , które są podłączane z boku, zastępujące samodzielne programatory urządzeń.Oprócz 8080 /8085, Intel wyprodukował szereg kompilatorów, w tym dla PL/M-80 i Pascala , oraz zestaw narzędzi do łączenia i statycznego lokalizowania programów, aby umożliwić ich zapisanie w EPROM i użycie w systemach wbudowanych .

Tańsza płyta „MCS-85 System Design Kit” (SDK-85) zawiera procesor 8085, pamięć ROM 8355 zawierającą program do monitorowania debugowania, pamięć RAM 8155 i 22 porty we/wy, klawiaturę szesnastkową 8279 i 8 cyfr 7 -segmentowa dioda LED oraz interfejs szeregowy pętli prądowej TTY (Teletype) 20 mA. Dostępne są pady dla jeszcze jednego EPROM 2K×8 8755, a opcjonalnie można dodać kolejny 256 bajtowy RAM 8155 I/O Timer/Counter. Wszystkie dane, sygnały sterujące i adresowe są dostępne na podwójnych złączach pinowych, a zapewniony jest duży obszar prototypowania.

Lista Intel 8085

| Numer modelu | Szybkośc zegara | Zakres temperatury | Data wydania | Cena (w dolarach amerykańskich) |

|---|---|---|---|---|

| 8085-2 | 5 MHz | |||

| ID8085 | 3 MHz | Przemysłowy | marzec/kwiecień 1979 | 38,75$ |

| M8085A | 3 MHz | Wojskowy | marzec/kwiecień 1979 | 110,00 zł |

Aplikacje

W celu szerokiego wykorzystania 8085 w różnych aplikacjach, mikroprocesor jest wyposażony w zestaw instrukcji składający się z różnych instrukcji, takich jak MOV, ADD, SUB, JMP itp. Instrukcje te są napisane w formie programu, który służy do wykonywania różnych operacje, takie jak rozgałęzianie, dodawanie, odejmowanie, operacje bitowe logiczne i operacje przesunięcia bitowego . Bardziej złożone operacje i inne operacje arytmetyczne muszą być zaimplementowane w oprogramowaniu. Na przykład mnożenie jest realizowane za pomocą algorytmu mnożenia .

Procesor 8085 był używany w kilku wczesnych komputerach osobistych, na przykład linia TRS-80 Model 100 wykorzystywała 80C85 firmy OKI (MSM80C85ARS). Wersja CMOS 80C85 procesora NMOS/HMOS 8085 ma kilku producentów. W Związku Radzieckim opracowano klon 80C85 pod oznaczeniem IM1821VM85A ( ros . ИМ1821ВМ85А ), który w 2016 r. był nadal w produkcji. Niektórzy producenci oferują warianty z dodatkowymi funkcjami, takimi jak dodatkowe instrukcje. Rad-hard wersja 8085 została w przetwarzających dane instrumentem na pokładzie przez kilka NASA i ESA kosmicznych misjach fizyki w 1990 i na początku 2000, w tym CRRES , Polar , FAST , Klastra , Hessi , w Sojourner Mars Rover i THEMIS . Szwajcarska firma SAIA używała 8085 i 8085-2 jako procesorów swojej linii programowalnych sterowników logicznych PCA1 w latach 80-tych.

Pro-Log Corp. umieścił 8085 i wspierający sprzęt na karcie formatu magistrali STD zawierającej procesor, pamięć RAM, gniazda ROM/EPROM, I/O i interfejsy magistrali zewnętrznej. Dołączona karta referencyjna zestawu instrukcji wykorzystuje zupełnie inne mnemoniki dla procesora Intel 8085. Produkt był bezpośrednim konkurentem oferty kart Multibus firmy Intel .

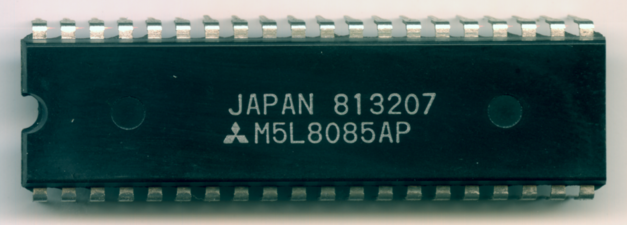

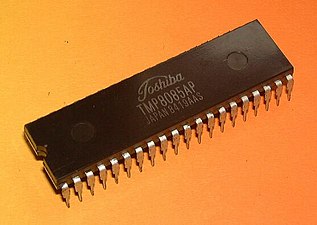

- Drugie źródła Intel 8085

AMD Am9085

Mitsubishi M5L8085

OKI M80C85

Siemens SAB8085

Toshiba TMP8085

Rodzina MCS-85

Procesor 8085 jest jedną z części rodziny chipów opracowanych przez firmę Intel do budowy kompletnego systemu. Wiele z tych układów obsługi było również używanych z innymi procesorami. Oryginalny IBM PC oparty na procesorze Intel 8088 używał kilku takich chipów; równoważne funkcje są dziś dostarczane przez układy VLSI , a mianowicie układy „ mostek południowy ”.

- 8085 – procesor

- 8155 — 2K-bitowa statyczna pamięć RAM MOS z 3 portami we/wy i zegarem. Wersja przemysłowa ID8155 była dostępna za 37,50 USD w ilościach po 100 i więcej. Wojskowa wersja M8155 była dostępna za 100,00 USD w ilościach po 100. Istnieje wersja 5 MHz Intel 8155-2.

- 8156 — 2K-bitowa statyczna pamięć RAM MOS z 3 portami we/wy i zegarem. Wersja przemysłowa ID8156 była dostępna za 37,50 USD w ilościach po 100 i więcej. Istnieje wersja 5 MHz Intel 8156-2.

- 8185 – 1024 x 8-bitowa statyczna pamięć RAM. Wersja 5 MHz Intel 8185-2 była dostępna za 48,75 USD w ilości 100 sztuk w ciągu 30 dni od otrzymania zamówienia.

- 8355 – 16,384-bit (2048 × 8) ROM z I/O. Wersja przemysłowa ID8355 była dostępna za 22,00 USD w ilościach 1000 lub więcej. Istnieje 5 MHz wersja Intel 8355-2.

- 8604 – 4096-bit (512 × 8) PROM

- 8755 – 2 KB przestrzeni adresowalnej EPROM, dwa porty 8-bitowe. Intel 8755A-2 to wersja 5 MHz. Ta wersja była dostępna za 81,00 USD w ilości 100 sztuk w ciągu 30 dni od otrzymania zamówienia. Była dostępna wersja produktu klasy przemysłowej Intel I8755A-8.

- 8202 — Kontroler dynamicznej pamięci RAM. Obsługuje następujące moduły Intel 2104A, 2117 lub 2118 DRAM. Ta wersja obsługuje również do 128 KB modułów DRAM. Cena została obniżona do 36,25 USD dla ilości 100 sztuk dla tych opakowań D8202 około maja 1979 roku.

- 8203 — Kontroler dynamicznej pamięci RAM. Wersja 82C03 CMOS Intela rozprasza mniej niż 25 mA. Obsługuje do 16x 64Kbit RAM o łącznej pojemności do 256KB. Odświeża się co 10 do 16 mikrosekund. Obsługuje multipleksowanie adresów pamięci wierszy i kolumn. Generuje stroboskopy, aby wewnętrznie zatrzasnąć adres. Arbitrażuje między równoczesnymi żądaniami dostępu do pamięci i odświeżenia. Potwierdza również cykle dostępu do pamięci do procesora systemu. 82C03 jest dostępny w opakowaniach ceramicznych lub plastikowych za 32 USD w ilości 100 sztuk.

- 8205 – 1 z 8 dekoderów binarnych

- 8206 – Jednostka wykrywania i korekcji błędów

- 8207 — Kontroler DRAM

- 8210 - TTL To MOS Shifter i sterownik zegara wysokiego napięcia

- 8212 – 8-bitowy port we/wy. Wersja przemysłowa ID8212 była dostępna za 6,75 USD w ilościach po 100 i więcej.

- 8216 — 4-bitowy sterownik magistrali równoległej dwukierunkowej. Wersja przemysłowa ID8216 była dostępna za 6,40 USD w ilościach po 100 i więcej.

- 8218/8219 – Kontroler magistrali

- 8226 — 4-bitowy sterownik magistrali równoległej dwukierunkowej. Wersja przemysłowa ID8226 była dostępna za 6,40 USD w ilościach po 100 i więcej.

- 8231 – Jednostka przetwarzania arytmetycznego

- 8232 — Procesor zmiennoprzecinkowy

- 8237 — Kontroler DMA

- 8251 – Kontroler komunikacji

- 8253 – Programowalny zegar interwałowy

- 8254 – Programowalny zegar interwałowy. Dostępna wersja 82C54 CMOS zostało zlecone Oki Electronic Industry Co., Ltd .

- 8255 – Programowalny interfejs peryferyjny

- 8256 – Wielofunkcyjne urządzenie peryferyjne. Układ ten łączy Intel 8251A Programowalny Interfejs komunikacyjny, Intel 8253 Programowalny interwalometr, Intel 8255A Programowalny Peripheral Interface, a Intel 8259A programowalny kontroler przerwań. Ten układ wykorzystuje wielofunkcyjne szeregowe , równoległy I / O , licznik / Wyłączniki i przerwań . Wersja Intel 8256AH była dostępna w cenie 21,40 USD za sztukę w ilościach po 100 sztuk.

- 8257 — Kontroler DMA

- 8259 – Programowalny kontroler przerwań

- 8271 – Programowalny kontroler dyskietek

- 8272 — Kontroler dyskietek o pojedynczej/podwójnej gęstości. Jest kompatybilny z formatami IBM 3740 i System 34 i zapewnia zarówno modulację częstotliwości (FM), jak i zmodyfikowaną modulację częstotliwości (MFM). Ta wersja jest dostępna za 38,10 USD w ilościach co najmniej 100.

- 8273 — Programowalny kontroler protokołu HDLC / SDLC . To urządzenie obsługuje protokół komunikacyjny ISO/ CCITT HDLC i IBM SDLC. Te wersje są dostępne w cenie 33,75 USD (4 MHz) i 30,00 USD (8 MHz) w ilościach co najmniej 100.

- 8274 — Wieloprotokołowy kontroler szeregowy

- 8275 — programowalny sterownik CRT. Ta funkcja wyświetla skanowanie rastrowe CRT. Jego funkcja odświeżania wyświetlacza poprzez buforowanie z pamięci głównej i śledzenie części wyświetlacza. Ta wersja jest dostępna za 32,00 USD w ilościach co najmniej 100.

- 8276 — Mały systemowy kontroler CRT

- 8278 — Programowalny interfejs klawiatury

- 8279 — Klawiatura/kontroler wyświetlacza

- 8282 – 8-bitowy nieodwracający zatrzask z buforem wyjściowym

- 8283 – 8-bitowy zatrzask odwracający z buforem wyjściowym

- 8291 – Rozmówca/słuchacz GPIB . Ten kontroler może pracować w zakresie od 1 do 8 MHz. Jest dostępny za 23,75 USD w ilościach co najmniej 100.

- 8292 — Kontroler GPIB. Zaprojektowany wokół Intel 8041A, który został zaprogramowany jako element interfejsu kontrolera. Kontroluje również magistralę za pomocą trzech zegarów blokady w celu wykrycia problemów na interfejsie magistrali GPIB. Jest dostępny za 21,25 USD w ilościach co najmniej 100.

- 8293 – Transceiver GPIB. Ten chipset obsługuje do 4 różnych trybów: Linie kontrolne mówcy/słuchacza w trybie 0, Linie kontrolne mówcy/słuchacza w trybie 1, Linie danych mówcy/słuchacza/kontrolera w trybie 2, Linie danych mówcy/słuchacza w trybie 3. Jest dostępny za 11,50 USD za sztukę w ilości 100 sztuk. W momencie wydania jest dostępny w próbkach, a następnie w pełnej produkcji w pierwszym kwartale 1980 roku.

- 8294 — Jednostka szyfrowania/deszyfrowania danych + 1 port O/P. Szyfruje i odszyfrowuje 64-bitowe bloki danych przy użyciu algorytmu Federal Information Processing Data Encryption Standard . Wykorzystuje to również algorytm szyfrowania National Bureau of Standards . Ten DEU działa przy użyciu 56-bitowego klucza określonego przez użytkownika do generowania 64-bitowych słów zaszyfrowanych. Jest dostępny za 22,50 USD w ilościach co najmniej 100.

- 8295 — Kontroler drukarki igłowej. Jest to interfejs z drukarkami igłowymi serii LRC 7040, a także używany do łączenia z innymi małymi drukarkami. Był dostępny za 20,65 USD w ilościach po 100 lub więcej.

Zastosowanie edukacyjne

W wielu szkołach inżynierskich procesor 8085 jest używany w kursach wprowadzających na temat mikroprocesorów. Zestawy szkoleniowe składające się z płytki drukowanej 8085 i sprzętu pomocniczego oferowane są przez różne firmy. Zestawy te zazwyczaj zawierają kompletną dokumentację pozwalającą studentowi przejść od lutowania do programowania w asemblerze w jednym kursie. Również architektura i zestaw instrukcji 8085 są łatwe do zrozumienia dla studenta. Wersje edukacyjne i hobbystyczne komputerów jednopłytowych z procesorem 8085 w ramach projektu Shared są wymienione poniżej w sekcji Linki zewnętrzne tego artykułu.

Symulatory

Dostępne są symulatory oprogramowania dla mikroprocesora 8085, które umożliwiają symulowane wykonywanie kodów operacji w środowisku graficznym.

Zobacz też

- IBM System/23 Datamaster umożliwił projektantom IBM zapoznanie się z chipami obsługującymi 8085 używanymi w IBM PC .

Uwagi

Bibliografia

Dalsza lektura

- Książki

- William Stallings Organizacja i Architektura Komputerów: Projektowanie pod kątem wydajności 8th Ed. Prentice Hall, 2009 ISBN 0-13-607373-5

- Mikroprocesor Abhishek Yadav 8085, 8086 Firewall Media, 2008 ISBN 81-318-0356-2

- Ramesh Gaonkar Architektura mikroprocesorowa, programowanie i aplikacje z 8085 Penram International Publishing ISBN 81-87972-09-2

- Bill Detwiler Tandy TRS-80 Model 100 Teardown Tech Republic, 2011 Web

- 8080A/8085 Programowanie w języku asemblera ; 1-sze wydanie; Lance Leventhal; Adam Osborne & Associates; 495 stron; 1978. (archiwum)

- Techniki interfejsu mikroprocesorowego ; 3. wydanie; Rodnay Zaks i Austina Lesae; Sybex; 466 stron; 1979; ISBN 978-0-89588-029-1 . (archiwum)

- Zrozumienie mikroprocesorów 8085/8086 i peryferyjnych układów scalonych poprzez pytania i odpowiedzi ; drugie wydanie; SK Sen; Międzynarodowe wydawnictwa New Age; 303 strony; 2010; ISBN 978-8122429749 . (archiwum)

- Karty referencyjne

- Karta referencyjna Intel 8085 ; Saudyjska; 2 strony. (archiwum)

Zewnętrzne linki

Symulatory:

- GNUSim8085 - symulator, asembler, debugger

Tablice: