Motorola 68040 - Motorola 68040

| Informacje ogólne | |

|---|---|

| Uruchomiona | 1990 |

| Zaprojektowany przez | Motorola |

| Występ | |

| Maks. Częstotliwość taktowania procesora | 25 MHz do 40 MHz |

| Szerokość danych | 32 bity |

| Szerokość adresu | 32 bity |

| Pamięć podręczna | |

| Pamięć podręczna L1 | 4096 bajtów dla instrukcji i danych z niezależnymi MMU i TLB |

| Architektura i klasyfikacja | |

| Zestaw instrukcji | Seria Motorola 68000 |

| Specyfikacje fizyczne | |

| Tranzystory | |

| Pakiet(y) | |

| Produkty, modele, warianty | |

| Warianty | |

| Historia | |

| Poprzednik | Motorola 68030 |

| Następca | Motorola 68060 |

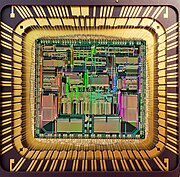

Motorola 68040 ( „ sześćdziesiąt osiem-oh-czterdzieści ”) jest mikroprocesor 32-bitowy w serii MC68000 , wydany w roku 1990. Jest następcą 68030 i następuje 68060 . Nie było 68050. Zgodnie z ogólnym nazewnictwem Motoroli, 68040 jest często określany po prostu jako '040 (wymawiane „ o-cztery-o” lub „ o-czterdzieści” ).

68040 był pierwszym członkiem rodziny 680x0 z wbudowanym układem zmiennoprzecinkowym (FPU). W ten sposób zawierał wszystkie funkcje, które wcześniej wymagały zewnętrznych chipów, a mianowicie jednostkę zarządzania FPU i pamięcią (MMU), która została dodana w 68030. Posiadał również rozdzielone pamięci podręczne instrukcji i danych po 4 kilobajty każda. Został on w pełni potokowym , z sześciu etapów.

Wersje 68040 zostały stworzone dla określonych segmentów rynku, w tym 68LC040 , która usunęła FPU i 68EC040 , która usunęła zarówno FPU, jak i MMU. Motorola przeznaczyła wariant EC do użytku wbudowanego, ale wbudowane procesory w czasach 68040 nie potrzebowały mocy 68040, więc warianty EC 68020 i 68030 nadal były powszechne w projektach.

Motorola wyprodukowała kilka klas szybkości. Części 16 MHz i 20 MHz nigdy nie zostały zakwalifikowane (oznaczenie XC) i użyte jako próbki prototypowe. W całej linii występowały stopnie 25 MHz i 33 MHz, ale do około 2000 r. stopień 40 MHz dotyczył tylko „pełnego” 68040. Planowana skala 50 MHz została anulowana po przekroczeniu dopuszczalnej obwiedni termicznej .

Stosowanie

W komputerach Apple Macintosh 68040 został wprowadzony w Macintoshu Quadra , który został nazwany na cześć chipa. Najszybszy procesor 68040 był taktowany z częstotliwością 40 MHz i był używany tylko w Quadra 840AV. Droższe modele z (krótkotrwałej) linii Macintosh Centris również używały 68040, podczas gdy tańsze Quadra, Centris i Macintosh Performa używały 68LC040 . 68040 był również używany w innych komputerach osobistych , takich jak Amiga 4000 i Amiga 4000T , a także w szeregu stacji roboczych , serwerach Alpha Microsystems , serii HP 9000/400 oraz nowszych wersjach komputera NeXT .

Projekt

68040 na wczesnym etapie projektowania znalazł się na granicy budżetu tranzystorów. Podczas gdy MMU nie zabierało wielu tranzystorów – w rzeczywistości, mając je na tej samej matrycy, co procesor faktycznie oszczędzał na tranzystorach – FPU z pewnością tak. Zewnętrzny FPU 68882 Motoroli był znany jako jednostka o bardzo wysokiej wydajności, a Motorola nie chciała ryzykować, że integratorzy używają wersji „LC” z 68882 zamiast bardziej opłacalnej pełnej jednostki „RC”. (Aby uzyskać informacje na temat modelu wieloprocesorowego Motoroli z serią 680x0, zobacz Motorola 68020 .) FPU w 68040 został w ten sposób pozbawiony funkcji transcendentalnych IEEE , które były obsługiwane zarówno przez 68881, jak i 68882 i były używane przez popularne oprogramowanie do generowania fraktali czasu i niewiele więcej. Pakiet wsparcia zmiennoprzecinkowego Motorola (FPSP) emulował te instrukcje w oprogramowaniu podczas przerwań. Ponieważ był to program obsługi wyjątków, intensywne korzystanie z funkcji transcendentalnych powodowało poważne obniżenie wydajności.

Upał zawsze był problemem przez całe życie 68040. Chociaż zapewniał ponad czterokrotnie wyższą wydajność na zegar niż 68020 i 68030, złożoność układu i wymagania dotyczące zasilania wynikały z dużej matrycy i dużej pamięci podręcznej. Wpłynęło to na skalowanie procesora i nigdy nie był w stanie pracować z częstotliwością zegara przekraczającą 40 MHz. Planowano wariant 50 MHz, ale anulowano. Entuzjaści przetaktowywania zgłosili sukces osiągający 50 MHz przy użyciu oscylatora 100 MHz zamiast części 80 MHz i nowej wówczas techniki dodawania przewymiarowanych radiatorów z wentylatorami.

68040 oferował te same funkcje, co Intel 80486 , ale w oparciu o zegar na zegar może znacznie przewyższyć układ Intela w instrukcjach całkowitych i zmiennoprzecinkowych.

Warianty

68EC040

68EC040 jest wersja MC68040 mikroprocesora, przeznaczonego dla wbudowanych kontrolerów (KE). Różni się od 68040 tym, że nie ma ani FPU, ani MMU. To sprawia, że jest tańszy i pobiera mniej energii. 68EC040 został użyty w przełączniku Cisco Supervisor Engine I, który jest sercem modeli 2900, 2948G, 2980G, 4000, 4500, 5000, 5500, 6000, 6500 i 7600.

68LC040

68LC040 jest niski koszt wersja Motorola 68040 mikroprocesor bez FPU. Dzięki temu jest tańszy i pobiera mniej energii. Chociaż procesor pasuje teraz do tabeli funkcji bardziej jak Motorola 68030, nadal zawiera pamięć podręczną i potok 68040, dzięki czemu jest znacznie szybszy niż 68030.

Niektóre wersje masek 68LC040 zawierały błąd, który uniemożliwiał prawidłowe działanie układu, gdy używany jest programowy emulator FPU . Według erraty Motoroli, żaden chip z zestawem masek 2E71M lub nowszym nie zawiera błędu. Ta nowa maska została wprowadzona w połowie 1995 roku i przekształciła chip 68LC040 do statusu MC.

Wadliwe wersje są zazwyczaj spotykane w komputerach Apple Macintosh opartych na 68LC040 . Chipy z zestawem masek 2E23G (używane w LC 475) zostały potwierdzone jako wadliwe. Błąd dotyczy utraty oczekujących zapisów w przypadku wyzwolenia wyjątku F-line. 68040 nie może zaktualizować swojego mikrokodu w sposób, w jaki współczesne układy x86. Oznacza to, że jedynym sposobem korzystania z oprogramowania wymagającego funkcji zmiennoprzecinkowych jest zastąpienie wadliwego 68LC040 nowszą wersją lub pełną 68040.

Tabela funkcji

| Wariant | MMU | FPU |

|---|---|---|

| 68040 | tak | tak |

| 68 LC 040 | tak | Nie |

| 68 WE 040 | Nie | Nie |

Dane techniczne

| Częstotliwość taktowania procesora | 25, 33, 40 MHz |

| Proces produkcji | statyczny CMOS 0,8 μm , 0,65 μm , Freescale 0,57 μm |

| Nośnik wiórów | 179 ceramicznych PGA i 184 QFP |

| Szyna adresowa | 32-bitowy |

| Magistrala danych | 32-bitowy |

| Zestaw instrukcji | CISC |

| Tranzystory | ~1200 000 |

ATC = pamięć podręczna tłumaczeń adresów

Bibliografia

Dalsza lektura

- Savard, John JG (2018) [2007]. „Wzorzec dziesiętny zmiennoprzecinkowy” . quadibloc . Inne najnowsze formaty dziesiętne zmiennoprzecinkowe. Zarchiwizowane od oryginału w dniu 3 lipca 2018 r . Źródło 16 lipca 2018 .

Linki zewnętrzne

- Strona podsumowania produktu MC68040

- MC68040V trzeciej generacji 32-bitowy mikroprocesor o niskim poborze mocy (PDF)

- Instrukcja obsługi mikroprocesorów M68040 (PDF)