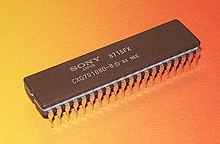

NEC V20 - NEC V20

NEC V20 (µPD70108), 8 MHz

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | Marzec 1984 |

| Wspólni producenci | |

| Wydajność | |

| Szerokość danych | 16 bitów |

| Specyfikacje fizyczne | |

| Tranzystory | |

| Rdzenie | |

| Współprocesor | |

NEC V20 był mikroprocesora przez NEC . Był zgodny zarówno z kodem PIN, jak i kodem obiektowym z Intel 8088 , z zestawem instrukcji podobnym do tego z Intel 80188 z pewnymi rozszerzeniami. V20 został wprowadzony w marcu 1984 roku.

Cechy

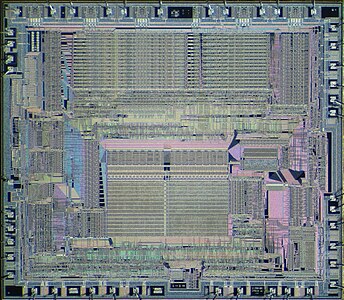

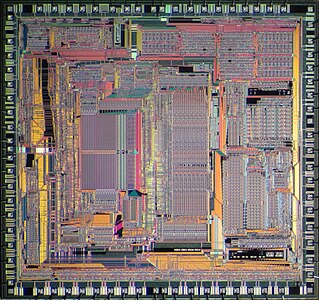

Matryca V20 składała się z 63 000 tranzystorów , ponad dwukrotnie więcej niż 29 000 procesora 8088. Układ został zaprojektowany z myślą o cyklu pracy zegara wynoszącym 50%, w porównaniu z 33% cyklem pracy używanym przez 8088. Wewnętrzne różnice oznaczały, że V20 może zazwyczaj wykonać więcej instrukcji w danym czasie niż Intel 8088 działający z tą samą częstotliwością.

V20 został wyprodukowany w 2-mikronowej technologii CMOS. Dostępne były wczesne wersje, które działały z szybkością 5, 8 i 10 MHz . W 1990 roku unowocześnienie technologii procesu produkcyjnego zaowocowało modelami V20H i V20HL o zwiększonej wydajności i zmniejszonym zużyciu energii. Późniejsze wersje dodały prędkości 12 i 16 MHz. V20HL były również całkowicie statyczne, co pozwalało na zatrzymanie ich zegara.

V20 został opisany jako 16-bitowy wewnętrznie. Używał 8-bitowej zewnętrznej szyny danych, która była multipleksowana na tych samych pinach, co niski bajt szyny adresowej. Jego 20-bitowa magistrala adresowa była w stanie zaadresować 1 MB.

Doniesiono, że V20 jest kompatybilny z koprocesorem Intel 8087 Floating Point Unit (FPU). NEC wyprodukował również swój własny FPU, μPD72091.

V30, prawie identyczny procesor z 16-bitową zewnętrzną szyną danych, zadebiutował 1 marca 1984 roku. Był zgodny z kodem pin i kodem obiektowym Intel 8086.

Rozszerzenia ISA

Architektura zestawu instrukcji V20 (ISA) zawierała kilka instrukcji nie wykonywanych przez 8088. Obejmowały one instrukcje dotyczące manipulacji bitami, spakowanych operacji BCD, mnożenia i dzielenia. Zawierały także nowe instrukcje trybu rzeczywistego z procesora Intel 80286.

Instrukcje ADD4S, SUB4S, i CMP4Sbyły w stanie dodawać, odejmować i porównywać ogromne upakowane, zakodowane binarnie liczby dziesiętne przechowywane w pamięci. Instrukcje ROL4i ROR4obracanie czterobitowych nibbles . Inną rodziną składał się z TEST1, SET1, CLR1i NOT1instrukcji, który to test, zestaw, jasne i odwracającego pojedynczych bitów ich operandów, ale są mniej efektywne niż później i80386 równoważników BT, BTS, BTRi BTC; nie są też kompatybilne ich kodowania. Były dwie instrukcje do wyodrębniania i wstawiania pól bitowych o dowolnej długości ( EXT, INS). I wreszcie pojawiły się dwa dodatkowe przedrostki powtórzeń, REPCi REPNC, które zmieniały oryginał REPEi REPNEinstrukcje skanowania ciągu bajtów lub słów (z instrukcjami SCASi CMPS), podczas gdy warunek mniejszy lub nie mniejszy pozostał spełniony.

V20 oferował tryb emulujący procesor Intel 8080 . BRKEMInstrukcja jest wydawany na rozpoczęcie 8080 emulacji. Operand instrukcji określa numer przerwania, którego wektor zawiera segment:offset, od którego ma się rozpocząć emulacja. Na koniec RETEMwydawana jest dyspozycja w kodzie 8080. Jedną z rzadko stosowanych funkcji jest CALLN(call native), która wydaje wywołanie przerwania typu 8086, które umożliwia IRETzmieszanie kodu x86 (który zwraca przy użyciu ) z kodem 8080.

Inny tryb wprowadza procesor w stan oszczędzania energii za pomocą HALTinstrukcji.

Pozew sądowy

W 1982 r. Intel pozwał firmę NEC za modele μPD8086 i μPD8088. Ten pozew został rozstrzygnięty poza sądem, a NEC zgodził się na licencjonowanie projektów od Intela.

Pod koniec 1984 r. Intel ponownie wniósł pozew przeciwko firmie NEC, twierdząc, że mikrokod w V20 i V30 naruszył jego patenty na procesory 8088 i 8086. Inżynier oprogramowania NEC, Hiroaki Kaneko, przestudiował zarówno projekt sprzętowy procesorów Intela, jak i oryginalny mikrokod Intela.

W swoim orzeczeniu sąd uznał, że mikrokod w magazynie kontrolnym stanowi program komputerowy, a więc jest chroniony prawem autorskim. Następnie odkryli, że Intel utracił swoje prawa autorskie, zaniedbując odpowiednie oznaczenie wszystkich chipów drugiego źródła. Sąd ustalił również, że NEC nie skopiował po prostu mikrokodu Intela i że mikrokod w V20 i V30 był wystarczająco różny od Intela, aby nie naruszać patentów Intela.

To orzeczenie ustanowiło legalność inżynierii odwrotnej.

Warianty i następcy

| Produkt: | Część nr: | Detale: |

|---|---|---|

| NEC V30 | μPD70116 | Zasadniczo NEC V20 z 16-bitową zewnętrzną magistralą danych, V30 był kompatybilny pinowo z Intel 8086 . V30 był fabrycznym ulepszeniem 8086 używanego w przełączniku centralnym GTD-5 EAX klasy 5. Był również używany w Psion Series 3 , NEC PC-9801 VM, Olivetti PCS86, Olivetti PC1, karcie Applied Engineering „PC Transporter” dla komputerów z serii Apple II oraz w różnych automatach arkadowych (szczególnie przez Irema ) pod koniec lat 80-tych. Wiele lat później w przenośnej konsoli do gier WonderSwan firmy Bandai zastosowano wersję niskonapięciową . |

| NEC V20HL | μPD70108H | Szybka (do 16 MHz) wersja V20 o niskim poborze mocy. |

| NEC V30HL | μPD70116H | Szybka (do 16 MHz) wersja V30 o niskim poborze mocy. |

| NEC V25 | µPD70320 | Wersja mikrokontrolera NEC V20. |

| NEC V25HS | μPD79011 | Wersja V25 z RX116 RTOS w wewnętrznej pamięci ROM. |

| NEC V25+ | μPD70325 | Szybka wersja V25. |

| NEC V33 | Wersja V30 z oddzielnymi magistralami adresowymi i danymi, której dekodowanie instrukcji odbywa się za pomocą logiki przewodowej, a nie mikroprogramowanej pamięci sterowania. Przepustowość jest dwukrotnie wyższa niż w przypadku V30 przy tej samej częstotliwości zegara. V33 ma wydajność odpowiadającą Intelowi 80286 . Przestrzeń adresowa pamięci została zwiększona do 16 MB. Dwie dodatkowe instrukcje BRKXAi RETXA, obsługują rozszerzony tryb adresowania. Emulacja 8080 nie jest obsługiwana.

|

|

| NEC V33A | μPD70136A | Różni się od V33 tym, że ma numery wektorów przerwań kompatybilne z procesorami Intel 80X86. |

| NEC V35 | μPD70330 | Wersja mikrokontrolera NEC V30. |

| NEC V35HS | μPD79021 | Wersja V35 z RX116 RTOS w wewnętrznej pamięci ROM. |

| NEC V35+ | μPD70335 | Szybka wersja V35. |

| NEC V40 | μPD70208 | Wbudowana wersja V20, zintegrowany 8251 USART zgodny z Intel , programowalny zegar interwałowy 8253 i interfejs portu równoległego 8255 . Używany w Olivetti PC1, Digisystems Jetta XD i Zenith EZ-PC. |

| NEC V40HL | μPD70208H | Szybka, niskonapięciowa wersja V40. |

| NEC V50 | μPD70216 | Wbudowana wersja V30. Jest to główny procesor w Akai S1000 i S1100 oraz Korg M1 . |

| NEC V50HL | μPD70216H | Szybka, niskonapięciowa wersja V50. |

| NEC V41 | μPD70270 | Integruje rdzeń V30HL i urządzenia peryferyjne PC-XT : interfejs portu równoległego 8255 , programowalny zegar interwałowy 8254 , 8259 PIC, kontroler DMA 8237 i kontroler klawiatury 8042 . Integruje również pełny kontroler DRAM. Był używany w Olivetti Quaderno XT-20. |

| NEC V51 | μPD70280 | Integruje rdzeń V30HL i urządzenia peryferyjne PC-XT : interfejs portu równoległego 8255 , programowalny zegar interwałowy 8254 , 8259 PIC, kontroler DMA 8237 i kontroler klawiatury 8042 . Integruje również pełny kontroler DRAM. Był używany w Olivetti Quaderno XT-20. |

| NEC V53 | μPD70236 | Integruje rdzeń V33 z 4-kanałowym DMA (μPD71087/i8237), UART (μPD71051/i8251), trzema timerami/licznikami (μPD71054/ i8254 ) i kontrolerem przerwań (μPD71059/ i8259 ). Był on używany w Akai MPC3000 i Akai SG01v . |

| NEC V53A | μPD70236A | Integruje niektóre urządzenia peryferyjne z rdzeniem V33A. |

| NEC V55PI | μPD70433 | |

| Vadem VG230 | Jednoukładowa platforma PC. VG230 zawierał procesor 16 MHz NEC V30HL i logikę zgodną z IBM PC/XT, kontroler LCD (CGA/AT&T640x400) z obsługą płaszczyzny dotykowej, skaner matrycy klawiatury, podwójny kontroler kart PCMCIA 2.1, obsługę sprzętu EMS 4.0 dla maksymalnie 64 MB oraz wbudowane kontrolery timera, PIC, DMA, UART i RTC. Był używany w HP OmniGo 100 , 120 i IBM Simon . | |

| Vadem VG330 | Następca VG230, zawierał 32-MHz procesor NEC V30MX i logikę rdzenia zgodną z IBM PC/AT z podwójnymi PIC, kontroler LCD (640x480), skaner matrycy klawiatury, kontroler PC Card ExCA 2.1 i port SIR. | |

| NEC V60 | Począwszy od procesora V60, NEC odszedł od konstrukcji x86. |

- Umierać zdjęcia

Zobacz też

- NEC RX116 , dedykowany 16-bitowy RTOS oparty na ITRON -1

- NEC μPD9002 , procesor kompatybilny z Z80 i x86

Bibliografia

Dalsza lektura

- Instrukcja obsługi V20/V30 ; NEC; 228 stron; 1986. (archiwum)

- Davis, Randy (grudzień 1985 – styczeń 1986). Napisany w Greenville, Teksas, USA. „Nowe mikroprocesory NEC — 8080, 8086 czy 8088?” (PDF) . Mikroróg obfitości (27). Bend, Oregon, USA: Micro Cornucopia Inc. s. 4-7. ISSN 0747-587X . Zarchiwizowane (PDF) od oryginału z dnia 2020-02-11 . Źródło 11.02.2020 .

Zewnętrzne linki

- Buchty, Rainer. „Kasiorama” . www.buchty.net .

- "NEC V20" . cpu-collection.de .

- Hinckley, Robert C. (styczeń 1987). „NEC v Intel. Will Hardware zostać wciągnięte przez czarną dziurę Redakcja praw autorskich " ” . Santa Clara High Technology Law Journal . Tom. 3 nie. 1. s. 23–72.