SIMM - SIMM

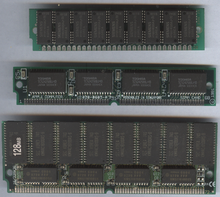

SIMM ( pojedynczy moduł pamięci in-line ) jest typu zawierającego moduł pamięci, pamięć o dostępie swobodnym używane w komputerach od 1980 do 2000 na początku. Różni się od dwurzędowego modułu pamięci (DIMM), najpopularniejszej formy modułu pamięci od późnych lat 90., tym, że styki na karcie SIMM są nadmiarowe po obu stronach modułu. Moduły SIMM zostały znormalizowane zgodnie ze standardem JEDEC JESD-21C.

Większość wczesnych płyt głównych do komputerów PC ( komputery z procesorami 8088 , XT i wczesne AT ) używały chipów DIP z gniazdami dla pamięci DRAM . Wraz ze wzrostem pojemności pamięci komputera zastosowano moduły pamięci, aby zaoszczędzić miejsce na płycie głównej i ułatwić rozbudowę pamięci. Zamiast podłączać osiem lub dziewięć pojedynczych chipów DIP, potrzebny był tylko jeden dodatkowy moduł pamięci, aby zwiększyć pamięć komputera.

Historia

Moduły SIMM zostały wynalezione w 1982 roku przez Jamesa J. Parkera w Zenith Microcircuits, a pierwszym klientem Zenith Microcircuits była firma Wang Laboratories . Wang Laboratories próbowało go opatentować i otrzymało patent w kwietniu 1987 roku. Patent ten został później unieważniony, gdy Wang Laboratories pozwało wiele firm o naruszenie, a następnie opublikowano, że były one wcześniejszym wynalazkiem Parkera w Zenith Microcircuits (Elk Grove Village, filia Zenith Electronics Corporation w stanie Illinois). Pozew został następnie wycofany i patent został unieważniony. Oryginalne moduły pamięci powstały na podłożach ceramicznych 64K Hitachi części „flip chip” i miał kołki, to znaczy pojedyncze opakowanie w linii (SIP) opakowania . Była część 8-bitowa i 9-bitowa, obie w 64K. Piny były najbardziej kosztowną częścią procesu montażu, a Zenith Microcircuits, w połączeniu z Wang i Amp, wkrótce opracował łatwe w montażu, bezpinowe złącze. Później moduły były budowane na podłożach ceramicznych z plastikowymi chipami Fujitsu J-lead, a jeszcze później na standardowym materiale PCB. Moduły SIMM wykorzystujące piny są zwykle nazywane modułami pamięci SIP lub SIPP , aby odróżnić je od bardziej popularnych modułów wykorzystujących złącza krawędziowe.

Pierwszy wariant modułów SIMM ma 30 pinów i zapewnia 8 bitów danych (plus dziewiąty bit wykrywania błędów w modułach SIMM z parzystością ). Były one używane w mikrokomputerach kompatybilnych z AT ( 286 , np. Wang APC ), 386 , 486 , Macintosh Plus , Macintosh II , Quadra , Atari STE , minikomputerach Wang VS oraz samplerach elektronicznych Roland .

Drugi wariant modułów SIMM ma 72 piny i zapewnia 32 bity danych (36 bitów w wersjach z parzystością i ECC ). Pojawiły się one najpierw na początku lat 90. w późniejszych modelach IBM PS/2 , a później w systemach opartych na 486 , Pentium , Pentium Pro , wczesnym Pentium II i współczesnych/konkurencyjnych chipach innych marek. W połowie lat 90. 72-pinowe moduły SIMM zastąpiły 30-stykowe moduły SIMM w nowo budowanych komputerach i zaczęły same być zastępowane przez moduły DIMM .

Komputery PC firm innych niż IBM, takie jak stacje robocze z systemem UNIX, mogą używać własnych, niestandardowych modułów SIMM. Macintosh IIfx używa zastrzeżonych niestandardowych SIMM z 64 pinami.

Technologie DRAM stosowane w modułach SIMM obejmują FPM (pamięć Fast Page Mode, używana we wszystkich 30-pinowych i wczesnych 72-pinowych modułach) oraz bardziej wydajną pamięć EDO DRAM (używaną w późniejszych modułach 72-pinowych).

Ze względu na różne szerokości szyn danych modułów pamięci i niektórych procesorów, czasami kilka modułów musi być zainstalowanych w identycznych parach lub w identycznych grupach po cztery, aby wypełnić bank pamięci. Zasadą jest 286 , 386SX , 68000 lub low-end 68020 / +68.030 (np Atari Falcon, Mac LC) System (za pomocą 16-bitową szynę danych) wymagałoby dwa 30-pinowe SIMM dla banku pamięci. W systemach 386DX , 486 i pełnej specyfikacji 68020 do 68060 (np. Atari TT, Amiga 4000, Mac II) (32-bitowa magistrala danych) dla jednego banku pamięci wymagane są albo cztery 30-pinowe moduły SIMM, albo jeden 72-pinowy SIMM. W systemach Pentium (szyna danych o szerokości 64 bitów) wymagane są dwie 72-pinowe moduły SIMM. Jednak niektóre systemy Pentium obsługują „tryb półbankowy”, w którym magistrala danych byłaby skrócona do zaledwie 32 bitów, aby umożliwić działanie pojedynczego modułu SIMM. Z drugiej strony, niektóre systemy 386 i 486 używają tak zwanego „przeplatania pamięci”, co wymaga dwukrotnie większej liczby modułów SIMM i skutecznie podwaja przepustowość.

Najwcześniejsze gniazda SIMM były konwencjonalnymi gniazdami typu push. Zostały one wkrótce zastąpione przez gniazda ZIF, w których SIMM był wkładany pod kątem, a następnie przechylany do pozycji pionowej. Aby usunąć jeden, dwa metalowe lub plastikowe klipsy na każdym końcu należy odciągnąć na bok, a następnie przechylić moduł SIMM do tyłu i wyciągnąć (gniazdo niskoprofilowe odwróciło nieco tę konwencję, podobnie jak moduły SODIMM - moduły są wkładane na " pod wysokim kątem, a następnie wciśnięty w dół, aby zrównać się z płytą główną). Wcześniejsze gniazda wykorzystywały plastikowe klipsy ustalające, które okazały się pękać, więc zastąpiły je stalowe klipsy.

Niektóre moduły SIMM obsługują wykrywanie obecności (PD). Do niektórych pinów, które kodują pojemność i prędkość modułu SIMM, nawiązywane są połączenia, dzięki czemu kompatybilny sprzęt może wykrywać właściwości modułu SIMM. Moduły PD SIMM mogą być używane w urządzeniach, które nie obsługują PD; informacja jest ignorowana. Standardowe moduły SIMM można łatwo przekonwertować do obsługi wyładowań niezupełnych, dopasowując zworki, jeśli moduły SIMM mają do tego pola lutownicze, lub przylutowując przewody.

30-pinowe moduły SIMM

Standardowe rozmiary: 256 KB, 1 MB, 4 MB, 16 MB

30-pinowe SIMMS-y mają 12 linii adresowych, które mogą zapewnić łącznie 24 bity adresu. Przy szerokości danych 8 bitów prowadzi to do absolutnej maksymalnej pojemności 16 MB zarówno dla modułów z parzystością, jak i bez parzystości (dodatkowy układ bitów redundancji zwykle nie przyczynia się do użytecznej pojemności).

| Pin # | Nazwa | Opis sygnału | Pin # | Nazwa | Opis sygnału | |

|---|---|---|---|---|---|---|

| 1 | V CC | +5 V DC | 16 | DQ4 | Dane 4 | |

| 2 | /CAS | Stroboskop adresu kolumny | 17 | A8 | Adres 8 | |

| 3 | DQ0 | Dane 0 | 18 | A9 | Adres 9 | |

| 4 | A0 | Adres 0 | 19 | A10 | Adres 10 | |

| 5 | A1 | Adres 1 | 20 | DQ5 | Dane 5 | |

| 6 | DQ1 | Dane 1 | 21 | /MY | Zapisz Włącz | |

| 7 | A2 | adres 2 | 22 | V SS | Ziemia | |

| 8 | A3 | Adres 3 | 23 | DQ6 | Dane 6 | |

| 9 | V SS | Ziemia | 24 | A11 | Adres 11 | |

| 10 | DQ2 | Dane 2 | 25 | DQ7 | Dane 7 | |

| 11 | A4 | Adres 4 | 26 | QP * | Wyłączenie parzystości danych | |

| 12 | A5 | Adres 5 | 27 | /RAZ | Stroboskop adresu wiersza | |

| 13 | DQ3 | Dane 3 | 28 | /CASP * | Stroboskop adresu kolumny parzystości | |

| 14 | A6 | Adres 6 | 29 | DP * | Parzystość danych w | |

| 15 | A7 | Adres 7 | 30 | V CC | +5 V DC |

* Piny 26, 28 i 29 nie są połączone w modułach SIMM bez kontroli parzystości.

72-pinowe moduły SIMM

Standardowe rozmiary: 1 MB, 2 MB, 4 MB, 8 MB, 16 MB, 32 MB, 64 MB, 128 MB (standard określa również moduły 3,3 V z dodatkowymi liniami adresowymi i do 2 GB)

Dzięki 12 liniom adresowym, które mogą zapewnić łącznie 24 bity adresu, dwóm szeregom chipów i 32-bitowemu wyjściu danych, absolutna maksymalna pojemność wynosi 2 27 = 128 MB.

| Pin # | Nazwa | Opis sygnału | Pin # | Nazwa | Opis sygnału | |

|---|---|---|---|---|---|---|

| 1 | V SS | Ziemia | 37 | MDP1 * | Parzystość danych 1 (MD8..15) | |

| 2 | MD0 | Dane 0 | 38 | MDP3 * | Parzystość danych 3 (MD24..31) | |

| 3 | MD16 | Dane 16 | 39 | V SS | Ziemia | |

| 4 | MD1 | Dane 1 | 40 | /CAS0 | Stroboskop adresu kolumny 0 | |

| 5 | MD17 | Dane 17 | 41 | /CAS2 | Stroboskop adresowy kolumny 2 | |

| 6 | MD2 | Dane 2 | 42 | /CAS3 | Stroboskop adresowy kolumny 3 | |

| 7 | MD18 | Dane 18 | 43 | /CAS1 | Stroboskop adresu kolumny 1 | |

| 8 | MD3 | Dane 3 | 44 | /RAS0 | Stroboskop adresu wiersza 0 | |

| 9 | MD19 | Dane 19 | 45 | /RAS1 † | Stroboskop adresu rzędu 1 | |

| 10 | V CC | +5 V DC | 46 | NC | Nie połączony | |

| 11 | NU [PD5 # ] | Nieużywane [Wykrywanie obecności 5 (3v3)] | 47 | /MY | Włącz odczyt/zapis | |

| 12 | MA0 | Adres 0 | 48 | NC [/ nr ECC ] | Brak połączenia [obecność ECC (jeśli uziemiony) (3v3)] | |

| 13 | MA1 | Adres 1 | 49 | MD8 | Dane 8 | |

| 14 | MA2 | adres 2 | 50 | MD24 | Dane 24 | |

| 15 | MA3 | Adres 3 | 51 | MD9 | Dane 9 | |

| 16 | MA4 | Adres 4 | 52 | MD25 | Dane 25 | |

| 17 | MA5 | Adres 5 | 53 | MD10 | Dane 10 | |

| 18 | MA6 | Adres 6 | 54 | MD26 | Dane 26 | |

| 19 | MA10 | Adres 10 | 55 | MD11 | Dane 11 | |

| 20 | MD4 | Dane 4 | 56 | MD27 | Dane 27 | |

| 21 | MD20 | Dane 20 | 57 | MD12 | Dane 12 | |

| 22 | MD5 | Dane 5 | 58 | MD28 | Dane 28 | |

| 23 | MD21 | Dane 21 | 59 | V CC | +5 V DC | |

| 24 | MD6 | Dane 6 | 60 | MD29 | Dane 29 | |

| 25 | MD22 | Dane 22 | 61 | MD13 | Dane 13 | |

| 26 | MD7 | Dane 7 | 62 | MD30 | Dane 30 | |

| 27 | MD23 | Dane 23 | 63 | MD14 | Dane 14 | |

| 28 | MA7 | Adres 7 | 64 | MD31 | Dane 31 | |

| 29 | MA11 | Adres 11 | 65 | MD15 | Dane 15 | |

| 30 | V CC | +5 V DC | 66 | NC [/EDO nr ] | Brak połączenia [obecność EDO (jeśli uziemiony) (3v3)] | |

| 31 | MA8 | Adres 8 | 67 | PD1 x | Wykrywanie obecności 1 | |

| 32 | MA9 | Adres 9 | 68 | PD2 x | Wykrywanie obecności 2 | |

| 33 | /RAS3 † | Stroboskop adresu rzędu 3 | 69 | PD3 x | Wykrywanie obecności 3 | |

| 34 | /RAS2 | Stroboskop adresu rzędu 2 | 70 | PD4 x | Wykrywanie obecności 4 | |

| 35 | MDP2 * | Parzystość danych 2 (MD16..23) | 71 | NC [PD (ref) # ] | Brak połączenia [Wykrywanie obecności (ref) (3v3)] | |

| 36 | MDP0 * | Parzystość danych 0 (MD0..7) | 72 | V SS | Ziemia |

* Styki 35, 36, 37 i 38 nie są połączone w modułach SIMM bez kontroli parzystości.

† /RAS1 i /RAS3 są używane tylko w dwurzędowych SIMMS: 2, 8, 32 i 128 MB.

# Te linie są zdefiniowane tylko w modułach 3.3V.

x Sygnały wykrywania obecności są szczegółowo opisane w standardzie JEDEC.

Zastrzeżone SIMM

64-stykowe GVP

Kilka kart procesorowych firmy Great Valley Products dla Commodore Amiga używało specjalnych 64-pinowych modułów SIMM (szerokość 32 bity, 1, 4 lub 16 MB, 60 ns).

Apple 64-pinowe

64-pinowe moduły SIMM z podwójnym portem były używane w komputerach Apple Macintosh IIfx, aby umożliwić nakładanie się cykli odczytu/zapisu (1, 4, 8, 16 MB, 80 ns).

| Pin # | Nazwa | Opis sygnału | Pin # | Nazwa | Opis sygnału | |

|---|---|---|---|---|---|---|

| 1 | GND | Ziemia | 33 | Q4 | Magistrala wyjściowa danych, bit 4 | |

| 2 | NC | Nie połączony | 34 | /W4 | Wejście umożliwiające zapis dla pamięci RAM IC 4 | |

| 3 | +5V | +5 woltów | 35 | A8 | Szyna adresowa, bit 8 | |

| 4 | +5V | +5 woltów | 36 | NC | Nie połączony | |

| 5 | /CAS | Stroboskop adresu kolumny | 37 | A9 | Szyna adresowa, bit 9 | |

| 6 | D0 | Magistrala wprowadzania danych, bit 0 | 38 | A10 | Szyna adresowa, bit 10 | |

| 7 | Q0 | Magistrala wyjściowa danych, bit 0 | 39 | A11 | Szyna adresowa, bit 11 | |

| 8 | /W0 | Wejście umożliwiające zapis dla pamięci RAM IC 0 | 40 | D5 | Magistrala wprowadzania danych, bit 5 | |

| 9 | A0 | Szyna adresowa, bit 0 | 41 | Q5 | Magistrala wyjściowa danych, bit 5 | |

| 10 | NC | Nie połączony | 42 | /W5 | Wejście umożliwiające zapis dla pamięci RAM IC 5 | |

| 11 | A1 | Szyna adresowa, bit 1 | 43 | NC | Nie połączony | |

| 12 | D1 | Magistrala wprowadzania danych, bit 1 | 44 | NC | Nie połączony | |

| 13 | Q1 | Magistrala wyjściowa danych, bit 1 | 45 | GND | Ziemia | |

| 14 | /W1 | Wejście umożliwiające zapis dla pamięci RAM IC 1 | 46 | D6 | Magistrala wprowadzania danych, bit 6 | |

| 15 | A2 | Szyna adresowa, bit 2 | 47 | Q6 | Magistrala wyjściowa danych, bit 6 | |

| 16 | NC | Nie połączony | 48 | /W6 | Wejście umożliwiające zapis dla pamięci RAM IC 6 | |

| 17 | A3 | Szyna adresowa, bit 3 | 49 | NC | Nie połączony | |

| 18 | GND | Ziemia | 50 | D7 | Magistrala wprowadzania danych, bit 7 | |

| 19 | GND | Ziemia | 51 | Q7 | Magistrala wyjściowa danych, bit 7 | |

| 20 | D2 | Magistrala wprowadzania danych, bit 2 | 52 | /W7 | Wejście umożliwiające zapis dla pamięci RAM IC 7 | |

| 21 | Q2 | Magistrala wyjściowa danych, bit 2 | 53 | /QB | Zarezerwowane (parzystość) | |

| 22 | /W2 | Wejście umożliwiające zapis dla pamięci RAM IC 2 | 54 | NC | Nie połączony | |

| 23 | A4 | Szyna adresowa, bit 4 | 55 | /RAZ | Stroboskop adresu wiersza | |

| 24 | NC | Nie połączony | 56 | NC | Nie połączony | |

| 25 | A5 | Szyna adresowa, bit 5 | 57 | NC | Nie połączony | |

| 26 | D3 | Magistrala wprowadzania danych, bit 3 | 58 | Q | Wyjście kontroli parzystości | |

| 27 | Q3 | Magistrala wyjściowa danych, bit 3 | 59 | /WWP | Napisz złą parzystość | |

| 28 | /W3 | Wejście umożliwiające zapis dla pamięci RAM IC 3 | 60 | PDCI | Wejście parzystości w łańcuchu | |

| 29 | A6 | Szyna adresowa, bit 6 | 61 | +5V | +5 woltów | |

| 30 | NC | Nie połączony | 62 | +5V | +5 woltów | |

| 31 | A7 | Szyna adresowa, bit 7 | 63 | PDCO | Parzystość wyjścia łańcuchowego | |

| 32 | D4 | Magistrala wprowadzania danych, bit 4 | 64 | GND | Ziemia |

HP LaserJet

72-pinowe moduły SIMM z niestandardowymi połączeniami wykrywania obecności (PD).

Zobacz też

- Pakiet dual-in-line (DIP)

- Pojedynczy pakiet in-line (SIP)

- Pakiet zygzakowaty w linii (ZIP)

- Podwójny moduł pamięci (DIMM)

Bibliografia

- ^ Patent USA 4,656,605 - Pojedynczy wbudowany moduł pamięci

- ^ Clayton, James E. (1983). Niedrogie opakowanie pamięci o dużej gęstości: moduł SIP 64K X 9 DRAM , The International Journal for hybrydowa mikroelektronika .

- ^ Wang gra silną rękę kompatybilną z komputerem PC , PC Magazine , 1 października 1985

- ^ Wykonywanie pracy standardowych modułów SIMM – Ulepszenie pamięci w HP LaserJet 6MP/5MP Artykuł o dopasowaniu zworek w celu dodania funkcji Presence Detect do standardowych modułów SIMM

- ^ JEDEC Standard nr 21-C, Sekcja 4.4.2 "72-pinowa rodzina modułów SIMM DRAM"

- ^ Macintosh IIfx

- ^ Komputer Apple, Inc. (1990). Przewodnik po sprzęcie rodziny Macintosh (wyd. 2). Addison-Wesley, Inc. 230.

- ^ Komputer Apple, Inc. (1990). Przewodnik po sprzęcie rodziny Macintosh (wyd. 2). Addison-Wesley, Inc. s. 214-222.