Zen (mikroarchitektura pierwszej generacji) - Zen (first generation microarchitecture)

Logo mikroarchitektury Zen to zamknięta ensō

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | 2 marca 2017 |

| Zaprojektowany przez | AMD |

| Wspólni producenci | |

| Kod CPUID | Rodzina 17h |

| Pamięć podręczna | |

| Pamięć podręczna L1 | Instrukcja 64 KB, dane 32 KB na rdzeń |

| Pamięć podręczna L2 | 512 KB na rdzeń |

| Pamięć podręczna L3 | 8 MB na czterordzeniowy CCX |

| Architektura i klasyfikacja | |

| Zestaw instrukcji | AMD64 (x86-64) |

| Specyfikacje fizyczne | |

| Tranzystory | |

| Rdzenie | |

| Gniazdo(a) | |

| Produkty, modele, warianty | |

| Nazwy kodów produktu | |

| Nazwy marek) | |

| Historia | |

| Poprzednik | Koparka (4. generacji) |

| Następca | Zen+ |

Zen to kryptonim pierwszej iteracji z rodziny mikroarchitektur procesorów komputerowych o tej samej nazwie od AMD . Po raz pierwszy został użyty z ich serią procesorów Ryzen w lutym 2017 roku. Pierwszy system podglądu oparty na Zen został zademonstrowany na targach E3 2016 , a po raz pierwszy został szczegółowo opisany na imprezie zorganizowanej jedną przecznicę od Intel Developer Forum 2016. Procesory o nazwie kodowej „Summit Ridge” pojawiły się na rynku na początku marca 2017 r., procesory serwerowe Epyc wywodzące się z Zen zostały wprowadzone na rynek w czerwcu 2017 r., a oparte na Zen APU pojawiły się w listopadzie 2017 r.

Zen to czysta konstrukcja, która różni się od poprzedniej, długoletniej architektury Bulldozer firmy AMD . Procesory oparte na Zen wykorzystują proces FinFET 14 nm , są podobno bardziej energooszczędne i mogą wykonywać znacznie więcej instrukcji na cykl . Wprowadzono SMT , dzięki czemu każdy rdzeń może obsługiwać dwa wątki. System pamięci podręcznej również został przeprojektowany, dzięki czemu pamięć podręczna L1 jest odpisywana . Procesory Zen używają trzech różnych gniazd: stacjonarne i mobilne układy Ryzen korzystają z gniazda AM4 , zapewniając obsługę DDR4 ; wysokiej klasy układy Threadripper do komputerów stacjonarnych oparte na Zen obsługują czterokanałową pamięć RAM DDR4 i oferują 64 linie PCIe 3.0 (w porównaniu z 24 liniami), korzystając z gniazda TR4 ; a procesory serwerowe Epyc oferują 128 linii PCI 3.0 i ośmiokanałową pamięć DDR4 przy użyciu gniazda SP3 .

Zen jest oparty na projekcie SoC . Kontrolery pamięci, PCIe, SATA i USB są wbudowane w ten sam układ scalony, co rdzenie procesora. Ma to zalety w zakresie przepustowości i mocy, kosztem złożoności układu i powierzchni matrycy. Ta konstrukcja SoC umożliwia skalowanie mikroarchitektury Zen od laptopów i niewielkich minikomputerów do wysokiej klasy komputerów stacjonarnych i serwerów.

Do 2020 roku AMD dostarczyło już 260 milionów rdzeni Zen.

Projekt

Według AMD głównym celem Zen jest zwiększenie wydajności na rdzeń. Nowe lub ulepszone funkcje obejmują:

- Pamięć podręczna L1 została zmieniona z zapisu przez zapis na zapis zwrotny, co pozwala na zmniejszenie opóźnień i większą przepustowość.

- Architektura SMT (simultaneous multithreading) pozwala na dwa wątki na rdzeń, co stanowi odejście od konstrukcji CMT (clustered multi-thread) stosowanej w poprzedniej architekturze Bulldozer . Jest to funkcja oferowana wcześniej w niektórych procesorach IBM , Intel i Oracle .

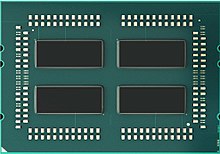

- Podstawowym budulcem wszystkich procesorów opartych na Zen jest Core Complex (CCX) składający się z czterech rdzeni i powiązanych z nimi pamięci podręcznych. Procesory z więcej niż czterema rdzeniami składają się z wielu CCX połączonych przez Infinity Fabric . Procesory o liczbie rdzeni innej niż wiele z czterech mają wyłączone niektóre rdzenie.

- Cztery jednostki ALU , dwie jednostki AGU / jednostki magazynujące i dwie jednostki zmiennoprzecinkowe na rdzeń.

- Nowo wprowadzona „duża” pamięć podręczna mikrooperacji .

- Każdy rdzeń SMT może wysłać do sześciu mikrooperacji na cykl (połączenie 6 mikrooperacji całkowitych i 4 mikrooperacji zmiennoprzecinkowych na cykl).

- Prawie 2 razy większa przepustowość L1 i L2, z 5-krotnie większą przepustowością pamięci podręcznej L3.

- Bramkowanie zegara .

- Większe kolejki na emeryturę, ładowanie i przechowywanie.

- Ulepszone przewidywanie rozgałęzień przy użyciu systemu haszowanego perceptronu z pośrednią tablicą docelową podobną do mikroarchitektury Bobcat, coś, co zostało porównane do sieci neuronowej przez inżyniera AMD Mike'a Clarka.

- Predyktor gałęzi jest oddzielony od etapu pobierania.

- Dedykowany silnik stosu do modyfikowania wskaźnika stosu , podobny do tego w procesorach Intel Haswell i Broadwell.

- Eliminacja ruchu — metoda, która ogranicza fizyczne przenoszenie danych w celu zmniejszenia zużycia energii.

-

Kompatybilność binarna z Intel Skylake (z wyłączeniem VT-x i prywatnych MSR):

- Obsługa RDSEED , zestawu instrukcji generatora liczb losowych o wysokiej wydajności wprowadzonego w Broadwell.

- Obsługa instrukcji SMAP , SMEP, XSAVEC/XSAVES/XRSTORS i CLFLUSHOPT.

- Wsparcie ADX .

- Wsparcie SHA .

- Instrukcja CLZERO do czyszczenia linii pamięci podręcznej. Przydatne do obsługi wyjątków kontroli maszyny związanych z ECC .

- PTE ( tabela na stronie wejścia) koalescencyjny , który łączy 4 kB tablic stron do 32 kB rozmiaru strony.

- „Czysta moc” (dokładniejsze czujniki monitorowania mocy).

- Obsługa pomiaru średniego limitu mocy podczas biegu (RAPL) w stylu Intel.

- Inteligentne pobieranie wstępne.

- Precyzyjne zwiększenie.

- eXtended Frequency Range (XFR), funkcja automatycznego przetaktowywania, która zwiększa częstotliwość taktowania poza reklamowaną częstotliwość turbo.

To pierwszy raz od bardzo dawna, kiedy my, inżynierowie, otrzymaliśmy całkowitą swobodę budowania procesora od podstaw i robienia wszystkiego, co w naszej mocy. To wieloletni projekt z naprawdę dużym zespołem. To jak maraton z kilkoma sprintami w środku. Zespół bardzo ciężko pracuje, ale widzą linię mety. Gwarantuję, że zapewni ogromną poprawę wydajności i zużycia energii w porównaniu z poprzednią generacją.

— Suzanne Plummer, lider zespołu Zen, 19 września 2015 r.

Architektura Zen opiera się na 14-nanometrowym procesie FinFET zleconym firmie GlobalFoundries , która z kolei licencjonuje swój 14- nanometrowy proces od Samsung Electronics . Daje to większą wydajność niż procesy 32 nm i 28 nm odpowiednio w poprzednich procesorach AMD FX i AMD APU . Rodzina procesorów Zen „Summit Ridge” wykorzystuje gniazdo AM4 i obsługuje DDR4 oraz 95 W TDP ( projektowa moc cieplna ). Chociaż nowsze mapy drogowe nie potwierdzają TDP dla produktów stacjonarnych, sugerują gamę produktów mobilnych o niskim poborze mocy z maksymalnie dwoma rdzeniami Zen o mocy od 5 do 15 W i od 15 do 35 W dla produktów mobilnych zorientowanych na wydajność z maksymalnie czterema rdzeniami Zen. rdzenie.

Każdy rdzeń Zen może dekodować cztery instrukcje na cykl zegara i zawiera pamięć podręczną mikrooperacyjną, która zasila dwa harmonogramy, po jednym dla segmentów całkowitych i zmiennoprzecinkowych . Każdy rdzeń ma dwie jednostki generowania adresu, cztery jednostki całkowite i cztery jednostki zmiennoprzecinkowe. Dwie jednostki zmiennoprzecinkowe to sumatory, a dwie to mnożące sumatory. Jednak użycie operacji wielokrotnego dodawania może uniemożliwić jednoczesne dodawanie w jednej z jednostek sumujących. Wprowadzono również ulepszenia w predyktorze gałęzi. Rozmiar pamięci podręcznej L1 wynosi 64 KB dla instrukcji na rdzeń i 32 KB dla danych na rdzeń. Rozmiar pamięci podręcznej L2 512 KB na rdzeń, a L3 to 1–2 MB na rdzeń. Pamięci podręczne L3 oferują 5-krotnie większą przepustowość niż poprzednie konstrukcje AMD.

Historia i rozwój

AMD zaczęło planować mikroarchitekturę Zen wkrótce po ponownym zatrudnieniu Jima Kellera w sierpniu 2012 roku. AMD oficjalnie ujawniło Zen w 2015 roku.

Zespół odpowiedzialny za Zen był kierowany przez Kellera (który odszedł we wrześniu 2015 po trzyletniej kadencji) i Zen Team Leader Suzanne Plummer. Głównym architektem Zen był starszy pracownik AMD Michael Clark.

Zen był pierwotnie planowany na 2017 rok po siostrzanym rdzeniu K12 opartym na ARM64 , ale podczas Dnia Analityka Finansowego AMD w 2015 roku ujawniono, że K12 został opóźniony na korzyść projektu Zen, aby umożliwić mu wejście na rynek w ramach czasowych 2016 roku, z premiera pierwszych procesorów opartych na Zen spodziewana w październiku 2016 r.

W listopadzie 2015 r. źródło wewnątrz AMD poinformowało, że mikroprocesory Zen zostały przetestowane i „spełniły wszystkie oczekiwania” bez „nie znaleziono znaczących wąskich gardeł”.

W grudniu 2015 r. pojawiły się pogłoski, że Samsung mógł zostać zatrudniony jako producent 14 nm procesorów FinFET AMD, w tym zarówno Zen, jak i nadchodzącej architektury GPU Polaris . Zostało to wyjaśnione przez ogłoszenie AMD z lipca 2016 r., że produkty zostały pomyślnie wyprodukowane w 14 nm procesie FinFET firmy Samsung. AMD stwierdziło, że Samsung będzie używany „w razie potrzeby”, argumentując, że zmniejszyłoby to ryzyko dla AMD poprzez zmniejszenie zależności od jednej odlewni.

W grudniu 2019 r. AMD zaczęło wypuszczać produkty Ryzen pierwszej generacji zbudowane przy użyciu architektury Zen+ drugiej generacji.

Przewaga nad poprzednikami

Proces produkcji

Procesory oparte na Zen wykorzystują 14 nm krzem FinFET . Te procesory są podobno produkowane w GlobalFoundries . Przed Zen, najmniejszy rozmiar procesu AMD wynosił 28 nm, co było wykorzystywane przez ich mikroarchitektury Steamroller i Excavator . Bezpośrednia konkurencja, mikroarchitektura Skylake i Kaby Lake firmy Intel, jest również wytwarzana na 14 nm FinFET; choć Intel planował rozpocząć wypuszczanie części 10 nm jeszcze w 2017 r. Intel nie był w stanie osiągnąć tego celu i w 2021 r. wyprodukowano tylko chipy mobilne w procesie 10 nm . W porównaniu do 14 nm FinFET Intela, AMD twierdziło w lutym 2017 r., że rdzenie Zen będą o 10% mniejsze. Intel ogłosił później w lipcu 2018 r., że procesorów głównego nurtu 10 nm nie należy się spodziewać przed drugą połową 2019 r.

W przypadku identycznych projektów te skurcze matrycy zużywają mniej prądu (i mocy) przy tej samej częstotliwości (lub napięciu). Ponieważ procesory mają zwykle ograniczoną moc (zwykle do ~125 W lub ~45 W w przypadku urządzeń mobilnych), mniejsze tranzystory pozwalają albo na niższą moc przy tej samej częstotliwości, albo wyższą częstotliwość przy tej samej mocy.

Wydajność

Jednym z głównych celów Zen w 2016 roku było skupienie się na wydajności na rdzeń i dążenie do 40% poprawy liczby instrukcji na cykl (IPC) w stosunku do swojego poprzednika. Dla porównania, Excavator oferował poprawę o 4–15% w stosunku do poprzednich architektur. AMD ogłosiło, że ostateczna mikroarchitektura Zen faktycznie osiągnęła 52-procentową poprawę w IPC w porównaniu z Excavatorem. Włączenie SMT umożliwia również każdemu rdzeniowi przetwarzanie do dwóch wątków, zwiększając przepustowość przetwarzania dzięki lepszemu wykorzystaniu dostępnych zasobów.

Procesory Zen wykorzystują również czujniki w układzie scalonym do dynamicznego skalowania częstotliwości i napięcia. Pozwala to na dynamiczne i automatyczne definiowanie maksymalnej częstotliwości przez sam procesor w oparciu o dostępne chłodzenie.

AMD zademonstrowało 8-rdzeniowy/16-wątkowy procesor Zen, który w testach renderowania Blender i HandBrake przewyższa równie taktowany procesor Intel Broadwell-E .

Zen obsługuje AVX2, ale wymaga dwóch cykli zegara, aby ukończyć każdą instrukcję AVX2 w porównaniu z instrukcją Intela. Ta różnica została skorygowana w Zen 2 .

Pamięć

Zen obsługuje pamięć DDR4 (do ośmiu kanałów) oraz ECC .

W raportach przedpremierowych stwierdzono, że jednostki APU korzystające z architektury Zen będą również obsługiwać pamięć o wysokiej przepustowości (HBM). Jednak pierwszy zademonstrowany APU nie wykorzystywał HBM. Poprzednie układy APU firmy AMD opierały się na pamięci współdzielonej zarówno dla GPU, jak i CPU.

Pobór mocy i moc grzewcza

Procesory zbudowane w węźle 14 nm na krzemie FinFET powinny wykazywać mniejsze zużycie energii, a zatem wydzielać ciepło w porównaniu do swoich poprzedników bez technologii FinFET o długości 28 nm i 32 nm (w przypadku równoważnych projektów) lub mieć większą moc obliczeniową przy równoważnej mocy cieplnej/zużyciu mocy.

Zen używa również bramkowania zegara , zmniejszając częstotliwość niewykorzystanych części rdzenia w celu oszczędzania energii. Pochodzi to z technologii AMD SenseMI, wykorzystującej czujniki w układzie do dynamicznego skalowania częstotliwości i napięcia.

Ulepszone zabezpieczenia i obsługa wirtualizacji

Zen dodał wsparcie dla Secure Memory Encryption (SME) AMD i Secure Encrypted Virtualization (SEV) AMD. Bezpieczne szyfrowanie pamięci to szyfrowanie pamięci w czasie rzeczywistym wykonywane na podstawie wpisu w tablicy stron. Szyfrowanie odbywa się w sprzętowym silniku AES, a klucze są zarządzane przez wbudowany procesor „Security” ( ARM Cortex-A5 ) podczas rozruchu, aby zaszyfrować każdą stronę, umożliwiając szyfrowanie dowolnej pamięci DDR4 (w tym nieulotnych). AMD SME sprawia również, że zawartość pamięci jest bardziej odporna na podsłuchiwanie pamięci i ataki typu cold boot .

SME może być używany do oznaczania poszczególnych stron pamięci jako zaszyfrowanych za pomocą tabel stron. Strona pamięci oznaczona jako zaszyfrowana zostanie automatycznie odszyfrowana podczas odczytu z DRAM i będzie automatycznie zaszyfrowana podczas zapisu do DRAM. Funkcja SME jest identyfikowana przez funkcję CPUID i włączana przez SYSCFG MSR. Po włączeniu, wpisy tablicy stron będą określać sposób dostępu do pamięci. Jeśli wpis tablicy strony ma ustawioną maskę szyfrowania pamięci, wówczas ta pamięć będzie dostępna jako pamięć zaszyfrowana. Maska szyfrowania pamięci (jak również inne powiązane informacje) jest określana na podstawie ustawień zwróconych przez tę samą funkcję CPUID, która identyfikuje obecność funkcji.

Funkcja Secure Encrypted Virtualization (SEV) umożliwia przejrzyste szyfrowanie zawartości pamięci maszyny wirtualnej za pomocą klucza unikalnego dla maszyny wirtualnej gościa. Kontroler pamięci zawiera wysokowydajny silnik szyfrowania, który można zaprogramować za pomocą wielu kluczy do użytku przez różne maszyny wirtualne w systemie. Programowanie i zarządzanie tymi kluczami jest obsługiwane przez oprogramowanie układowe AMD Secure Processor, które udostępnia interfejs API do tych zadań.

Łączność

Włączając większość mostka południowego do SoC , procesor Zen zawiera łącza SATA , USB i PCI Express NVMe . Można to uzupełnić dostępnymi chipsetami Socket AM4, które dodają opcje łączności, w tym dodatkowe złącza SATA i USB oraz obsługę AMD Crossfire i Nvidia SLI .

AMD, ogłaszając swoją linię Radeon Instinct, argumentowało, że nadchodzący procesor serwerowy Naples oparty na Zen będzie szczególnie odpowiedni do budowania systemów głębokiego uczenia . 128 linii PCIe na procesor Naples pozwala ośmiu kartom Instinct połączyć się przez PCIe x16 z pojedynczym procesorem. Jest to korzystne w porównaniu z linią Intel Xeon, która ma tylko 40 linii PCIe.

Cechy

Procesory

APU

Produkty

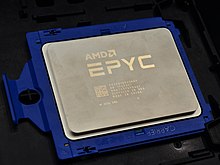

Architektura Zen jest wykorzystywana w obecnej generacji desktopowych procesorów Ryzen . Jest również w procesorach serwerowych Epyc (następca procesorów Opteron ) i APU.

Zgodnie z planem AMD, pierwsze procesory do komputerów stacjonarnych bez procesorów graficznych (o nazwie kodowej „Summit Ridge”) miały trafić do sprzedaży pod koniec 2016 roku; z pierwszymi procesorami mobilnymi i stacjonarnymi typu AMD Accelerated Processing Unit (o nazwie kodowej „Raven Ridge”), które pojawiły się pod koniec 2017 r. AMD oficjalnie opóźniło Zen do pierwszego kwartału 2017 r. W sierpniu 2016 r. wczesna demonstracja architektury pokazała 8-rdzeniowy /16-wątkowa próbka inżynierska procesora przy 3,0 GHz.

W grudniu 2016 r. AMD oficjalnie ogłosiło, że linia procesorów do komputerów stacjonarnych pod marką Ryzen zostanie wydana w pierwszym kwartale 2017 r. Potwierdziła również, że procesory serwerowe zostaną wydane w drugim kwartale 2017 r., a mobilne APU w drugiej połowie 2017 r.

2 marca 2017 r. AMD oficjalnie wprowadziło na rynek pierwsze ośmiordzeniowe procesory Ryzen oparte na architekturze Zen. Ostateczne prędkości zegara i TDP dla 3 procesorów wydane w pierwszym kwartale 2017 r. wykazały znaczną poprawę wydajności na wat w porównaniu z poprzednią architekturą K15h (Piledriver) . Ośmiordzeniowe procesory Ryzen do komputerów stacjonarnych wykazały wydajność na wat porównywalną z ośmiordzeniowymi procesorami Intel Broadwell.

W marcu 2017 r. AMD zademonstrowało również próbkę inżynieryjną procesora serwerowego opartego na architekturze Zen. Procesor (o nazwie kodowej „Neapol”) został skonfigurowany jako platforma serwerowa z dwoma gniazdami, przy czym każdy procesor ma 32 rdzenie/64 wątki.

Procesory do komputerów stacjonarnych

| Model | Data wydania i cena |

Wspaniałe | Chiplety |

Rdzenie ( wątki ) |

Konfiguracja podstawowa | Częstotliwość zegara ( GHz ) | Pamięć podręczna | Gniazdo elektryczne |

PCIe pasy (Użytkownik dostępny + chipset Link) |

Obsługa pamięci | TDP | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Baza |

OPP 1-2 (≥3) |

XFR 1-2 |

L1 | L2 | L3 | ||||||||||

| Poziom podstawowy | |||||||||||||||

| Ryzen 3 1200 |

27 lipca 2017 US $109 |

GloFo 14LP |

1 × CCD | 4 (4) | 2 × 2 | 3.1 | 3.4 (3.1) |

3.45 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

2 × 4 MB na CCX |

AM4 | 24 (20+4) | DDR4-2667 dwukanałowy |

65 W |

| Ryzen 3 Pro 1200 |

27 lipca 2017 OEM |

3.1 | 3,4 (?) |

? | |||||||||||

| Ryzen 3 Pro 1300 |

27 lipca 2017 OEM |

3,5 | 3,7 (?) |

? | |||||||||||

| Ryzen 3 1300X |

27 lipca 2017 US $129 |

3,5 | 3,7 (3,5) |

3,9 | |||||||||||

| Główny nurt | |||||||||||||||

| Ryzen 5 1400 |

11 kwietnia 2017 US $169 |

GloFo 14LP |

1 × CCD | 48) | 2 × 2 | 3.2 | 3.4 (3.4) |

3.45 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

2 × 4 MB na CCX |

AM4 | 24 (20+4) | DDR4-2667 dwukanałowy |

65 W |

| Ryzen 5 Pro 1500 |

11 kwietnia 2017 OEM |

3,5 | 3,7 (?) |

? | 2 × 8 MB na CCX |

||||||||||

| Ryzen 5 1500X |

11 kwietnia 2017 US $189 |

3,5 | 3,7 (3,6) |

3,9 | |||||||||||

| Ryzen 5 1600 |

11 kwietnia 2017 US $219 |

6 (12) | 2 × 3 | 3.2 | 3,6 (3,4) |

3,7 | |||||||||

| Ryzen 5 Pro 1600 |

11 kwietnia 2017 OEM |

3.2 | 3,6 (?) |

? | |||||||||||

| Ryzen 5 1600X |

11 kwietnia 2017 US $249 |

3,6 | 4.0 (3.7) |

4.1 | 95 W | ||||||||||

| Wydajność | |||||||||||||||

| Ryzen 7 1700 |

2 marca 2017 329 USD |

GloFo 14LP |

1 × CCD | 8 (16) | 2 × 4 | 3.0 | 3,7 (3,2) |

3,75 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

2 × 8 MB na CCX |

AM4 | 24 (20+4) | DDR4-2667 dwukanałowy |

65 W |

| Ryzen 7 Pro 1700 |

2 marca 2017 OEM |

3.4 | 3,8 (?) |

? | |||||||||||

| Ryzen 7 1700X |

2 marca 2017 399 USD |

3.4 | 3,8 (3,5) |

3,9 | 95 W | ||||||||||

| Ryzen 7 1800X |

2 marca 2017 499 USD |

3,6 | 4.0 (3.7) |

4.1 | |||||||||||

| Komputer stacjonarny wysokiej klasy (HEDT) | |||||||||||||||

| Ryzen Threadripper 1900X |

31 sierpnia 2017 549 USD |

GloFo 14LP |

2 × CCD | 8 (16) | 2 × 4 | 3,8 | 4.0 (3.9) |

4.2 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

2 × 8 MB na CCX |

TR4 | 64 (60+4) | DDR4-2667 quad kanałowy |

180 W |

| Ryzen Threadripper 1920X |

10 sierpnia 2017 799 USD |

12 (24) | 4 × 3 | 3,5 | 4.0 | 4.2 | 4 × 8 MB na CCX |

||||||||

| Ryzen Threadripper 1950X |

10 sierpnia 2017 US $999 |

16 (32) | 4 × 4 | 3.4 | 4.0 (3.7) |

4.2 | |||||||||

Komputerowe APU

Jednostki APU Ryzen są oznaczone w nazwie przyrostkiem G lub GE.

| Model | Data wydania i cena |

Wspaniałe | procesor | GPU | Gniazdo elektryczne | PCIe pasy |

DDR4 pamięci wsparcie |

TDP (W) |

||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Rdzenie ( wątki ) |

Częstotliwość zegara ( GHz ) | Pamięć podręczna | Model | Konfiguracja | Zegar (GHz) |

Przetwarzania mocy ( GFLOPS ) |

||||||||||

| Baza | Zwiększyć | L1 | L2 | L3 | ||||||||||||

| Athlon 200GE | 6 września 2018 $55 |

GloFo 14LP |

2 (4) | 3.2 | Nie dotyczy | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

4 MB | Wega 3 | 192:12:4 3 zł |

1,0 | 384 | AM4 | 16 (8+4+4) | 2667 dwukanałowy |

35 |

| Athlon Pro 200GE | 6 września 2018 OEM |

|||||||||||||||

| Athlon 220GE | 21 grudnia 2018 65 USD |

3.4 | ||||||||||||||

| Athlon 240GE | 21 grudnia 2018 75 USD |

3,5 | ||||||||||||||

| Athlon 3000G | 19 listopada 2019 49 USD |

1,1 | 424,4 | |||||||||||||

| Athlon 300GE | 7 lipca 2019 OEM |

3.4 | ||||||||||||||

| Athlon Srebrny 3050GE | 21 lipca 2020 OEM |

|||||||||||||||

| Ryzen 3 2200 GE | 19 kwietnia 2018 OEM |

4 (4) | 3.2 | 3,6 | Wega 8 | 512:32:16 8 zł |

1126 | 2933 dwukanałowy |

||||||||

| Ryzen 3 Pro 2200GE | 10 maja 2018 OEM |

|||||||||||||||

| Ryzen 3 2200G | 12 lutego 2018 99 USD |

3,5 | 3,7 | 45- 65 |

||||||||||||

| Ryzen 3 Pro 2200G | 10 maja 2018 OEM |

|||||||||||||||

| Ryzen 5 2400 GE | 19 kwietnia 2018 OEM |

48) | 3.2 | 3,8 | RX Vega 11 | 704:44:16 | 1,25 | 1760 | 35 | |||||||

| Ryzen 5 Pro 2400GE | 10 maja 2018 OEM |

|||||||||||||||

| Ryzen 5 2400G | 12 lutego 2018 US $169 |

3,6 | 3,9 | 45- 65 |

||||||||||||

| Ryzen 5 Pro 2400G | 10 maja 2018 OEM |

|||||||||||||||

Mobilne APU

| Model | Data wydania |

Wspaniałe | procesor | GPU | Gniazdo elektryczne | PCIe pasy | Obsługa pamięci | TDP | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Rdzenie ( wątki ) |

Częstotliwość zegara ( GHz ) | Pamięć podręczna | Model | Konfiguracja | Zegar | Przetwarzania mocy ( GFLOPS ) |

||||||||||

| Baza | Zwiększyć | L1 | L2 | L3 | ||||||||||||

| Athlon Pro 200U | 2019 |

GloFo 14LP |

2 (4) | 2,3 | 3.2 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

4 MB | Wega 3 | 192:12:4 3 zł |

1000 MHz | 384 | PR5 | 12 (8+4) | DDR4-2400 dwukanałowy |

12–25 W |

| Athlon 300U | 6 stycznia 2019 | 2,4 | 3,3 | |||||||||||||

| Ryzen 3 2200U | 8 stycznia 2018 | 2,5 | 3.4 | 1100 MHz | 422,4 | |||||||||||

| Ryzen 3 3200U | 6 stycznia 2019 | 2,6 | 3,5 | 1200 MHz | 460,8 | |||||||||||

| Ryzen 3 2300U | 8 stycznia 2018 | 4 (4) | 2,0 | 3.4 | Wega 6 | 384:24:8 6 zł |

1100 MHz | 844,8 | ||||||||

| Ryzen 3 Pro 2300U | 15 maja 2018 r. | |||||||||||||||

| Ryzen 5 2500U | 26 października 2017 | 48) | 3,6 | Wega 8 | 512:32:16 8 zł |

1126.4 | ||||||||||

| Ryzen 5 Pro 2500U | 15 maja 2018 r. | |||||||||||||||

| Ryzen 5 2600H | 10 września 2018 r. | 3.2 | DDR4-3200 dwukanałowy |

35–54 W | ||||||||||||

| Ryzen 7 2700U | 26 października 2017 | 2.2 | 3,8 | Wega 10 | 640:40:16 10 zł |

1300 MHz | 1664 | DDR4-2400 dwukanałowy |

12–25 W | |||||||

| Ryzen 7 Pro 2700U | 15 maja 2018 r. | |||||||||||||||

| Ryzen 7 2800H | 10 września 2018 r. | 3,3 | Wega 11 | 704:44:16 11 zł |

1830.4 | DDR4-3200 dwukanałowy |

35–54 W | |||||||||

Procesory wbudowane

W lutym 2018 r. AMD ogłosiło serię V1000 wbudowanych jednostek APU Zen+Vega z czterema jednostkami SKU.

| Model | Data wydania |

Wspaniałe | procesor | GPU | DDR4 pamięci wsparcie |

Ethernet | TDP |

Temperatura złącza (°C) |

||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Rdzenie (wątki) |

Częstotliwość zegara ( GHz ) | Pamięć podręczna | Model | Konfiguracja | Zegar (GHz) |

Przetwarzania mocy ( GFLOPS ) |

||||||||||

| Baza | Zwiększyć | L1 | L2 | L3 | ||||||||||||

| V1500B | grudzień 2018 |

GloFo 14LP |

48) | 2.2 | Nie dotyczy | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

4 MB | Nie dotyczy | 2400 dwukanałowy |

2× 10GbE | 12–25 W | 0–105 | |||

| V1780B | 3,35 | 3,6 | 3200 dwukanałowy |

35–54 W | ||||||||||||

| V1202B | Luty 2018 | 2 (4) | 2,3 | 3.2 | RX Vega 3 | 192:12:16 3 zł |

1,0 | 384 | 2400 dwukanałowy |

12–25 W | ||||||

| V1404I | grudzień 2018 | 48) | 2,0 | 3,6 | RX Vega 8 | 512:32:16 8 zł |

1,1 | 1126.4 | -40 – 105 | |||||||

| V1605B | Luty 2018 | 0–105 | ||||||||||||||

| V1756B | 3,25 | 1,3 | 1331.2 | 3200 dwukanałowy |

35–54 W | |||||||||||

| V1807B | 3,35 | 3,8 | RX Vega 11 | 704:44:16 11 zł |

1830.4 | |||||||||||

Procesory serwerowe

AMD ogłosiło w marcu 2017 roku, że w drugim kwartale tego roku wypuści platformę serwerową opartą na Zen o nazwie kodowej Naples. Platforma obejmuje systemy 1- i 2-gniazdowe. Procesory w konfiguracjach wieloprocesorowych komunikują się za pośrednictwem technologii AMD Infinity Fabric. Każdy układ obsługuje osiem kanałów pamięci i 128 linii PCIe 3.0, z czego 64 linie są używane do komunikacji CPU-CPU za pośrednictwem Infinity Fabric w przypadku instalacji w konfiguracji dwuprocesorowej. AMD oficjalnie ujawniło Neapol pod marką Epyc w maju 2017 roku.

20 czerwca 2017 r. AMD oficjalnie zaprezentowało procesory z serii Epyc 7000 podczas premiery w Austin w Teksasie.

| Model | Data wydania i cena |

Wspaniałe | Chiplety |

Rdzenie (wątki) |

Podstawowa konfiguracja | Częstotliwość zegara ( GHz ) | Pamięć podręczna | Gniazdo i konfiguracja |

PCIe Lanes |

Obsługa pamięci |

TDP | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Baza | Zwiększyć | L1 | L2 | L3 | |||||||||||

| Wszystkie rdzenie | Maks. | ||||||||||||||

| EPYC 7351P | Czerwiec 2017 750 . USD |

14 mil morskich | 4 × CCD | 16 (32) | 8 × 2 | 2,4 | 2,9 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

64 MB 8 MB na CCX |

SP3 1P |

128 | DDR4-2666 8 kanałów |

155/170 W | |

| EPYC 7401P | Czerwiec 2017 1075 USD |

24 (48) | 8 × 3 | 2,0 | 2,8 | 3.0 | |||||||||

| EPYC 7551P | Czerwiec 2017 US $2100 |

32 (64) | 8 × 4 | 2,55 | 180 W | ||||||||||

| EPYC 7251 | Czerwiec 2017 475 . USD |

8 (16) | 8 × 1 | 2,1 | 2,9 | 32 MB 8 MB na CCX |

SP3 2P |

DDR4-2400 8 kanałów |

120 W | ||||||

| EPYC 7261 | Połowa 2018 US $700+ |

2,5 | 64 MB 8 MB na CCX |

DDR4-2666 8 kanałów |

155/170 W | ||||||||||

| EPYC 7281 | Czerwiec 2017 650 . USD |

16 (32) | 8 × 2 | 2,1 | 2,7 | 32 MB 8 MB na CCX |

|||||||||

| EPYC 7301 | Czerwiec 2017 US $800+ |

2.2 | 64 MB 8 MB na CCX |

||||||||||||

| EPYC 7351 | Czerwiec 2017 US $1100+ |

2,4 | 2,9 | 2,9 | |||||||||||

| EPYC 7371 | Późny 2018 US $1550+ |

3.1 | 3,6 | 3,8 | 180 W | ||||||||||

| EPYC 7401 | Czerwiec 2017 US $1850 |

24 (48) | 8 × 3 | 2,0 | 2,8 | 3.0 | 155/170 W | ||||||||

| EPYC 7451 | Czerwiec 2017 US $2400+ |

2,3 | 2,9 | 3.2 | 180 W | ||||||||||

| EPYC 7501 | Czerwiec 2017 3400 USD |

32 (64) | 8 × 4 | 2,0 | 2,6 | 3.0 | 155/170 W | ||||||||

| EPYC 7551 | Czerwiec 2017 3400 USD+ |

2,55 | 180 W | ||||||||||||

| EPYC 7571 | Późno 2018 N / A |

2.2 | ? | 200 W? | |||||||||||

| EPYC 7601 | Czerwiec 2017 4200 USD |

2,7 | 3.2 | 180 W | |||||||||||

Procesory do serwerów wbudowanych

W lutym 2018 r. AMD ogłosiło również serię wbudowanych procesorów Zen EPYC 3000.

| Model | Data wydania |

Wspaniałe | Chiplety |

Rdzenie ( wątki ) |

Podstawowa konfiguracja | Częstotliwość zegara ( GHz ) | Pamięć podręczna | Gniazdo elektryczne |

PCIe pasy |

Ethernet |

Obsługa pamięci |

TDP | Temperatura złącza (°C) | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Baza | Zwiększyć | L1 | L2 | L3 | |||||||||||||

| Wszystkie rdzenie | Maks. | ||||||||||||||||

| EPYC 3101 | Luty 2018 | 14 mil morskich | 1 x CCD | 4 (4) | 1 × 4 | 2,1 | 2,9 | 2,9 | 64 KB inst. 32 KB danych na rdzeń |

512 KB na rdzeń |

8 MB | SP4r2 | 32 | 4 × 10GbE | DDR4-2666 dwukanałowy |

35 W | 0-95 |

| EPYC 3151 | 48) | 2 × 2 | 2,7 | 2,9 | 2,9 | 16 MB 8 MB na CCX |

45 W | ||||||||||

| EPYC 3201 | 8 (8) | 2 × 4 | 1,5 | 3.1 | 3.1 | DDR4-2133 dwukanałowy |

30 W | ||||||||||

| EPYC 3251 | 8 (16) | 2,5 | 3.1 | 3.1 | DDR4-2666 dwukanałowy |

55 W | 0-105 | ||||||||||

| EPYC 3255 | Nieznany | 25-55 W | -40-105 | ||||||||||||||

| EPYC 3301 | Luty 2018 | 2 x CCD | 12 (12) | 4 × 3 | 2,0 | 2.15 | 3.0 | 32 MB 8 MB na CCX |

64 | 8 × 10GbE | DDR4-2666 quad kanałowy |

65 W | 0-95 | ||||

| EPYC 3351 | 12 (24) | 1,9 | 2,75 | 3.0 | SP4 | 60-80 W | 0-105 | ||||||||||

| EPYC 3401 | 16 (16) | 4 × 4 | 1.85 | 2,25 | 3.0 | SP4r2 | 85 W | ||||||||||

| EPYC 3451 | 16 (32) | 2.15 | 2,45 | 3.0 | SP4 | 80-100W | |||||||||||

Zobacz też

Bibliografia

Zewnętrzne linki

- Procesory Ryzen – AMD