UltraSPARC - UltraSPARC

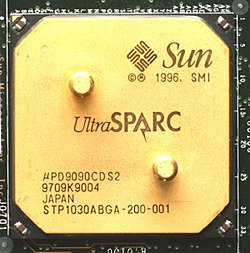

A 200 MHz UltraSPARC mikroprocesor

| |

| Wytworzony | Od 1995 do 1997 roku |

|---|---|

| Zaprojektowany przez | Sun Microsystems |

| Max. CPU częstotliwość zegara | 143 MHz do 200 MHz |

| zestaw instrukcji | SPARC V9 |

| rdzenie | 1 |

| Poprzednik | SuperSPARC II |

| Następca | UltraSPARC II |

UltraSPARC to mikroprocesorowy opracowany przez Sun Microsystems i wytwarzane przez Texas Instruments , wprowadzony w połowie 1995 roku. Jest to pierwszy mikroprocesor od Słońca do wdrożenia 64-bitowy SPARC V9 zestaw instrukcji architektury (ISA). Marc Tremblay był współtwórcą microarchitect.

Zawartość

mikroarchitektury

UltraSPARC to cztery problem Superskalarna mikroprocesor, który wykonuje instrukcje w na zamówienie . Ma dziewięć stadium całkowitą rurociągu .

jednostki funkcjonalne

Jednostki wykonawcze zostały uproszczone w stosunku do SuperSPARC osiągnąć wyższe częstotliwości zegara - przykład uproszczenia jest to, że nie ALU kaskadowo, w przeciwieństwie do SuperSPARC, aby uniknąć ograniczenia częstotliwości zegara.

Liczba całkowita plik rejestru ma 32 wpisy 64-bitowych. Jak SPARC ISA wykorzystuje okna rejestrów , z których UltraSPARC ma osiem, rzeczywista liczba rejestrów jest 144. Plik rejestr ma siedem i trzy porty odczytu i zapisu. Plik zawiera rejestry rejestr całkowitą dwóch jednostka arytmetyczno-logiczna oraz jednostki ładowania / zapisu. Dwie ALU można wykonać zarówno arytmetyczne, logiczne i przesunięcie wskazówek, ale tylko jeden może wykonać mnożenie i dzielenie instrukcje.

Jednostka zmiennoprzecinkowa składa się z pięciu jednostek funkcjonalnych. Aż podamy zmiennoprzecinkowych dodaje i odejmuje, mnoży, jeden jeden podziały i kwadratowe korzenie. Dwie jednostki są do wykonywania instrukcji SIMD zdefiniowane przez Zestaw audiowizualny Instruction (VIS). Plik rejestr zmiennoprzecinkowy zawiera trzydzieści dwa rejestry 64-bitowe. Posiada pięć portów czytać i trzy porty zapisu.

Pamięć podręczna

UltraSPARC posiada dwa poziomy pamięci podręcznej, pierwotnym i wtórnym. Istnieją dwa podstawowe bufory, jeden dla instrukcji i jeden dla danych. Obie mają pojemność 16 KB.

UltraSPARC wymaga obowiązkowego zewnętrznego cache wtórnego. Pamięć podręczna jest jednolita, ma pojemność 512 KB do 4 MB i jest bezpośrednim odwzorowane. To może zwracać dane w jednym cyklu. Cache zewnętrzna jest realizowany przy taktowaniu synchronicznym SRAM o tej samej częstotliwości jak mikroprocesor, a stosunki nie obsługiwane. Jest ona dostępna za pośrednictwem magistrali danych.

Produkcja

Zawierała ona 3,8 miliona tranzystorów. Został on wytworzony w procesie EPIC-3 Texas Instruments, 0,5 um komplementarną metal-tlenek-półprzewodnik procesu (CMOS) z czterema poziomami metalu. UltraSPARC nie zostało wykonane w BiCMOS procesu jak Texas Instruments twierdził, że nie skala procesów dobrze do 0,5 um, a oferowane niewielką poprawę wydajności. Proces ten został udoskonalony w TI MVP procesora sygnału cyfrowego (DSP) dla niektórych cech brakujących tak jak trzy poziomy metalu zamiast w czterech i wielkości 0,55 funkcji, przed jej stosować do wytwarzania UltraSparcm uniknąć powtarzania problemów produkcyjnych napotykanych SuperSPARC .

Pakiet

UltraSPARC pakuje się w 521 styku plastik tablicy siatki kulki (PBGA).

Powiązane procesory

Referencje

- Greenley, D. i in. (1995). "UltraSPARC: nowej generacji superskalarna 64-bitowy SPARC". Obrady Compcon '95 : pp. 442-451.

- Gwennap, Linley (3 października 1994). "UltraSparc Wyzwala SPARC Performance". Mikroprocesor Report , tom 8, liczba 13.

- Gwennap, Linley (05 grudnia 1994). „UltraSparc Dodaje instrukcje multimedialne”. Mikroprocesor Report .