Pixel Visual Core - Pixel Visual Core

Pixel wizualny Rdzeń ( PVC ) to seria ARM systemu w opakowaniu (SIP) procesorów graficznych zaprojektowanych przez Google . PVC to w pełni programowalna wielordzeniowa architektura specyficzna dla domeny (DSA) obrazu , wizji i sztucznej inteligencji dla urządzeń mobilnych, aw przyszłości dla IoT . Po raz pierwszy pojawił się w Google Pixel 2 i 2 XL, które zostały wprowadzone 19 października 2017 r. Pojawił się również w Google Pixel 3 i 3 XL . Począwszy od Pixela 4, ten układ został zastąpiony rdzeniem neuronowym Pixel .

Historia

Google poprzednio używany Qualcomm Snapdragon „s CPU , GPU , IPU oraz DSP do obsługi jej przetwarzania obrazu dla ich Google Nexus i Google Pixel urządzeń. Wraz ze wzrostem znaczenia technik fotografii komputerowej , Google opracował Pixel Visual Core (PVC). Google twierdzi, że obwód PVC zużywa mniej energii niż przy użyciu procesora i procesora graficznego, a jednocześnie jest w pełni programowalny, w przeciwieństwie do układu scalonego specyficznego dla aplikacji (ASIC) z jednostką tensorową (TPU ). Rzeczywiście, klasyczne urządzenia mobilne wyposażają procesor sygnału obrazu (ISP), który jest potokiem przetwarzania obrazu o stałej funkcjonalności . W przeciwieństwie do tego, PVC ma elastyczną programowalną funkcjonalność, nie ograniczającą się tylko do przetwarzania obrazu.

PVC w Google Pixel 2 i 2 XL jest oznaczony jako SR3HX X726C502.

PVC w Google Pixel 3 i 3 XL jest oznaczony jako SR3HX X739F030.

Dzięki PVC Pixel 2 i Pixel 3 uzyskały mobilny DxOMark 98 i 101. Ten ostatni był najwyżej notowanym pojedynczym obiektywem w teście DxOMark, na równi z iPhone'em XR.

Oprogramowanie Pixel Visual Core

Typowy program do przetwarzania obrazu PVC jest napisany w halogenku . Obecnie obsługuje tylko podzbiór języka programowania Halide bez operacji zmiennoprzecinkowych i z ograniczonymi wzorcami dostępu do pamięci. Halide to język specyficzny dla domeny, który pozwala użytkownikowi oddzielić algorytm od harmonogramu jego wykonania. W ten sposób programista może napisać program zoptymalizowany pod kątem docelowej architektury sprzętowej.

Pixel Visual Core ISA

PVC ma dwa typy architektury zestawu instrukcji (ISA) , wirtualną i fizyczną. Najpierw program w języku wysokiego poziomu jest kompilowany do wirtualnego ISA (vISA) , zainspirowanego RISC-V ISA, który całkowicie abstrahuje od docelowej generacji sprzętu. Następnie program vISA jest kompilowany do tzw. Fizycznego ISA (pISA) , czyli VLIW ISA. Ten krok kompilacji bierze pod uwagę docelowe parametry sprzętowe (np. Tablicę rozmiaru PE, rozmiar STP itp.) I wyraźnie określa ruchy pamięci. Oddzielenie Visa i Pisa pozwala pierwszą osobą, która być przekrój architektury i generowanie niezależne, a Piza mogą być zestawiane w trybie offline lub przez JIT kompilacji .

Architektura Pixel Visual Core

Pixel Visual Core został zaprojektowany jako skalowalna wielordzeniowa energooszczędna architektura, składająca się z parzystych liczb od 2 do 16 rdzeni. Rdzeniem PVC jest jednostka przetwarzania obrazu (IPU), programowalna jednostka dostosowana do przetwarzania obrazu. Architektura Pixel Visual Core została również zaprojektowana jako własny chip, taki jak SR3HX, lub jako blok IP dla System on a chip (SOC) .

Jednostka przetwarzania obrazu (IPU)

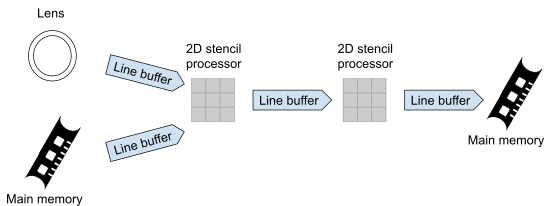

Rdzeń IPU zawiera procesor wzorcowy (STP), pulę buforów linii (LBP) i NoC . STP zapewnia głównie dwuwymiarową macierz SIMD elementów przetwarzających (PE) zdolnych do wykonywania obliczeń szablonowych , niewielkiego sąsiedztwa pikseli. Chociaż wydaje się podobny do skurczowej tablicy i obliczeń na froncie fali, STP ma wyraźny kontrolowany programowo ruch danych. Każdy PE zawiera 2x 16-bitowe arytmetyczne jednostki logiczne (ALU) , 1x 16-bitową jednostkę mnożnika z akumulatorem (MAC) , 10x 16-bitowych rejestrów i 10x 1-bitowe rejestry predykatów.

Pula buforów linii (LBP)

Biorąc pod uwagę, że jedną z najbardziej kosztownych energetycznie operacji jest dostęp do DRAM, każdy STP ma tymczasowe bufory zwiększające lokalność danych , a mianowicie LBP. Używany LBP to dwuwymiarowy FIFO, który obsługuje różne rozmiary odczytu i zapisu. LBP wykorzystuje model behawioralny jednego producenta dla wielu konsumentów. Każdy LBP może mieć osiem logicznych pamięci LB i jedną do operacji wejścia-wyjścia DMA . Ze względu na naprawdę dużą złożoność systemu pamięci, projektanci PVC określają sterownik LBP jako jeden z najtrudniejszych elementów. Zastosowany NoC to sieć pierścieniowa na chipie, używana do komunikacji tylko z sąsiednimi rdzeniami w celu oszczędzania energii i zachowania schematu obliczeniowego potokowego.

Procesor szablonów (STP)

STP ma dwuwymiarową macierz PE: na przykład macierz 16x16 pełnych PE i cztery tory uproszczonych PE zwanych „halo” . STP ma procesor skalarny, zwany linią skalarną (SCL), który dodaje instrukcje sterujące z małą pamięcią instrukcji. Ostatnim składnikiem STP jest jednostka magazynująca ładunki zwana generatorem arkuszy (SHG), gdzie arkusz jest modułem dostępu do pamięci PVC.

Podsumowanie projektu SR3HX

SR3HX PVC zawiera 64-bitowy procesor ARMv8a ARM Cortex-A53 , 8 rdzeni jednostki przetwarzania obrazu (IPU), 512 MB LPDDR4 , MIPI, PCIe. Każdy rdzeń IPU ma 512 jednostek arytmetyczno-logicznych (ALU) składających się z 256 elementów przetwarzających (PE) ułożonych w dwuwymiarową tablicę 16 x 16. Te rdzenie wykonują niestandardowy VLIW ISA. Istnieją dwie 16-bitowe jednostki ALU na element przetwarzający i mogą one działać na trzy różne sposoby: niezależne, połączone i skondensowane. SR3HX PVC jest produkowany jako SiP przez TSMC w procesie 28HPM HKMG . Został zaprojektowany przez ponad 4 lata we współpracy z firmą Intel . (Nazwa kodowa: Monette Hill) Google twierdzi, że SR3HX PVC jest 7-16x bardziej energooszczędny niż Snapdragon 835 . A że SR3HX PVC może wykonać 3 biliony operacji na sekundę, HDR + może działać 5 razy szybciej i zużywać mniej niż jedną dziesiątą energii niż Snapdragon 835 . Obsługuje Halide do przetwarzania obrazu i TensorFlow do uczenia maszynowego. Obecny układ działa z częstotliwością 426 MHz, a pojedynczy IPU jest w stanie wykonać więcej niż 1 TeraOPS.

Bibliografia

- ^ a b c Cutress, Ian. „Hot Chips 2018: The Google Pixel Visual Core Live Blog (10:00 PT, 17:00 UTC)” . www.anandtech.com . Źródło 02.02.2019 .

- ^ a b c d e f g h i j Hennessy, John; Patterson, David (2017). Architektura komputera: podejście ilościowe (wyd. Szóste). Morgan Kaufmann. pp. 579–606. ISBN 978-0-12-811905-1 .

- ^ „Google Pixel 2 XL Teardown” . iFixit . 2017-10-19 . Źródło 02.02.2019 .

- ^ „Google Pixel 3 XL Teardown” . iFixit . 2018-10-16 . Źródło 02.02.2019 .

- ^ „Pixel 2 DxOMark” .

- ^ „Pixel 3 DxOMark” .

- ^ „iPhone XR DxOMark” .

- ^ a b c d „The Pixel Visual Core: w pełni programowalny procesor Google do przetwarzania obrazu, wizji i sztucznej inteligencji dla urządzeń mobilnych. HotChips2018” (PDF) .

- ^ „Pixel Visual Core (PVC) - Google - WikiChip” . en.wikichip.org . Źródło 02.02.2019 .

- ^ „Współpraca Google i Intel w zakresie układu Pixel Visual Core w Pixelu 2” . xda-developerzy . 2017-10-25 . Źródło 02.02.2019 .

- ^ a b „Pixel Visual Core: przetwarzanie obrazu i uczenie maszynowe na Pixelu 2” . Google . 2017-10-17 . Źródło 02.02.2019 .