Elektrochemiczna pamięć RAM - Electrochemical RAM

Elektrochemiczna pamięć o dostępie swobodnym (ECRAM) to rodzaj pamięci nieulotnej (NVM) z wieloma poziomami na komórkę (MLC) zaprojektowany do akceleracji analogowej głębokiego uczenia . Ogniwo ECRAM to urządzenie z trzema końcówkami składające się z kanału przewodzącego, izolującego elektrolitu , zbiornika jonowego i metalowych styków. Rezystancja kanału jest modulowana przez wymianę jonową na styku kanału i elektrolitu po przyłożeniu pola elektrycznego. Proces przenoszenia ładunku pozwala zarówno na zachowanie stanu przy braku przyłożonej mocy, jak i na programowanie wielu różnych poziomów, różniących działanie ECRAM od tranzystora polowego (FET) . Operacja zapisu jest deterministyczna i może skutkować symetrycznym wzmocnieniem i depresją, czyniąc macierze ECRAM atrakcyjnymi do działania jako sztuczne wagi synaptyczne w fizycznych implementacjach sztucznych sieci neuronowych (ANN) . Wyzwania technologiczne obejmują potencjał obwodu otwartego (OCP) i zgodność półprzewodników z odlewnią związaną z materiałami energetycznymi. Uniwersytety, laboratoria rządowe i korporacyjne zespoły badawcze przyczyniły się do rozwoju ECRAM do obliczeń analogowych . Warto zauważyć, że Sandia National Laboratories zaprojektowało ogniwo na bazie litu inspirowane materiałami akumulatorów półprzewodnikowych, Uniwersytet Stanford zbudował ogniwo organiczne na bazie protonów, a firma International Business Machines (IBM) zademonstrowała programowanie równoległe bez selektora w pamięci do zadania regresji logistycznej w tablicy ECRAM z tlenku metalu przeznaczonej do umieszczenia w tylnym końcu linii (BEOL) .

Operacja

Pisać

Naprężenie na bramkę, w stosunku do elektrod kanałowych, może być przyłożone w postaci stałego prądu lub polaryzacji, kierując jony w kierunku lub od interfejsu elektrolit/kanał, gdzie następuje transfer ładunku przy swobodnych nośnikach. Po wprowadzeniu do kanału ładunek jonowy jest neutralizowany, a formy atomowe interkalują lub wiążą się z przewodzącą macierzą gospodarza, w niektórych przypadkach powodując odkształcenie i zlokalizowaną transformację fazową. Takie odwracalne procesy są równoważne reakcjom anodowo-katodowym w ogniwach baterii lub urządzeniach elektrochromowych . Chociaż w ECRAM programowanie elementu pamięci nie jest definiowane jako zmiana pojemności lub nieprzezroczystości, ale przez zmianę przewodnictwa kanału związanego z wstawianiem lub usuwaniem form atomowych w wyniku sygnału stresu.

Czytać

Operacja odczytu jest oddzielona od operacji zapisu dzięki obecności trzech elektrod, co ogranicza zakłócenia odczytu. Pomiędzy elektrodami kanału występuje niewielkie napięcie polaryzacji, dzięki czemu odczytywany prąd jest proporcjonalny do przewodności kanału, dzięki czemu wykrywa zaprogramowany stan urządzenia.

Prędkość

Szybkość programowania komórek ECRAM nie jest ograniczona masową dyfuzją jonów. W rzeczywistości muszą jedynie przekroczyć płaszczyznę styku między elektrolitem a kanałem, aby wywołać zmianę przewodności. Nanosekundowe impulsy zapisu mogą rzeczywiście wywołać programowanie. Kompromisy między pojemnością bramki , przewodnością elektronową itp. mogą generować przejściowe stany nieustalone, ograniczając maksymalną częstotliwość odczytu i zapisu.

Tablice

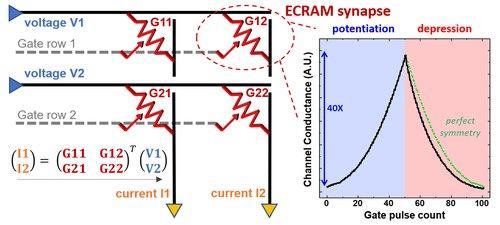

Macierze ECRAM są zintegrowane w układzie pseudo-crossbar, linia dostępu do bramki jest wspólna dla wszystkich urządzeń w rzędzie lub kolumnie. Jeśli zmiana potencjału elektrochemicznego , siły napędowej baterii, nastąpi w wyniku wymiany jonowej między kanałem a elektrodą bramki, na styku bramki występuje potencjał obwodu otwartego (OCP) i będzie on różnił się między urządzeniami w zależności od zaprogramowanego stanu. Aby zapobiec przenikowi między komórkami współdzielącymi linię bramkową, urządzenie dostępowe izolujące każdą z nich jest dodawane szeregowo z elementem pamięci. Tłumienie OCP w projekcie ECRAM, minimalizuje rozmiar/złożoność komórki, pozwalając na równoległy odczyt/programowanie macierzy urządzeń bez selektora.

Funkcja synaptyczna

Zasada

Pamięć nieulotną (NVM) można wykorzystać do obliczeń w pamięci , zmniejszając w ten sposób częstotliwość przesyłania danych między jednostkami pamięci masowej i przetwarzania. Może to ostatecznie poprawić czas obliczeniowy i wydajność energetyczną w porównaniu z hierarchiczną architekturą systemu, eliminując wąskie gardło Von Neumanna . W związku z tym, stosując komórki wielopoziomowe (MLC) w węzłach macierzy cross-bar, można wykonywać operacje analogowe na danych zakodowanych w czasie lub napięciu, takich jak wektor (sygnał wejściowy wiersza) × macierz (matryca pamięci). Zgodnie z prawami Kirchoffa i Ohma uzyskany wektor jest następnie otrzymywany przez całkowanie prądu zebranego w każdej kolumnie. W przypadku komórek ECRAM w każdym wierszu dodawana jest dodatkowa linia w celu zapisania komórek podczas cykli programowania, tworząc w ten sposób architekturę pseudo-krzyżową. W dziedzinie sztucznej inteligencji (AI) , głębokie sieci neuronowe (dnn) są wykorzystywane do klasyfikacji i zadań uczenia się, opierając się na dużej liczbie operacji mnożenia macierzy,. Dlatego obliczenia analogowe z technologią NVM do takich zadań są niezwykle atrakcyjne. Komórki ECRAM są wyjątkowo pozycjonowane do stosowania w analogowych akceleratorach głębokiego uczenia ze względu na ich nieodłączną deterministyczną i symetryczną naturę programowania w porównaniu z innymi urządzeniami, takimi jak rezystancyjna pamięć RAM (ReRAM lub RRAM) i pamięć zmiany fazy (PCM) .

Wymagania

| Metryczny | Jednostka | Docelowa komórka synaptyczna NVM |

|---|---|---|

| Zakres G | nS | 9-72 |

| stosunek wł./wył. | nie | 8 |

| # stanów | nie | 1000 |

| asymetria góra/dół | % | 5 |

| czas napisać | ns | 1 |

Fizyczna implementacja sztucznych sieci neuronowych (ANN) musi działać z izodokładnością w porównaniu z wagami dokładności zmiennoprzecinkowej w oprogramowaniu. Wyznacza to granicę dla właściwości urządzeń potrzebnych dla analogowych akceleratorów głębokiego uczenia . Firma IBM Research opublikowała takie wymagania przy projektowaniu jednostki przetwarzania rezystancyjnego (RPU), których podzbiór znajduje się tutaj. Wspólne projektowanie algorytmów i sprzętu może je nieco rozluźnić, ale nie bez innych kompromisów.

Użycie NVM jako wag synaptycznych zamiast przechowywania oznacza znacznie różne wymagania, jeśli chodzi o docelowy zakres oporu, liczbę poziomów oraz szybkość i symetrię programowania. Ponieważ obliczenia w pamięci odbywają się równolegle przez macierz, wiele urządzeń jest adresowanych jednocześnie i dlatego muszą mieć wysoką średnią rezystancję, aby ograniczyć rozpraszanie energii. Aby wykonać obliczenia o wysokiej dokładności i być odpornym na szum, komórka NVM potrzebuje dużej liczby odrębnych stanów. Czas programowania musi być szybki tylko między poziomami, a nie od najwyższych do najniższych stanów oporu. Podczas każdego cyklu programowania ( propagacja wsteczna ) aktualizacje wag mogą być ujemne lub dodatnie, a zatem wykresy w górę/w dół wymagają symetrii, aby umożliwić zbieżność algorytmów uczenia się. Wszystkie technologie NVM mają problemy z tymi celami. Poszczególne komórki ECRAM mogą spełniać tak rygorystyczne wskaźniki, ale muszą również wykazywać wydajność macierzy o wysokiej gęstości i stochastyczność.

Prezentacje z macierzami synaptycznymi ECRAM

Sandia National Laboratories

Jak donosi w 2019 roku w Science, Elliot J. Fuller, Alec A. Talin i in. z Sandia National Laboratories we współpracy ze Stanford University i University of Massachusetts Amherst :

Wykorzystując współpłaszczyznowe organiczne komórki wielopoziomowe, izolowane przez urządzenia z przewodzącą pamięcią mostkową (CBM), zespół demonstruje równoległe programowanie i adresowanie w maksymalnie 3×3 macierzach. W szczególności dwuwarstwowa sieć neuronowa jest mapowana do macierzy poprzez przeniesienie wag niezbędnych do wykonania zadania wnioskowania, co skutkuje operacją XOR na binarnym wektorze wejściowym.

Poszczególne komórki mają następujące właściwości (nie wszystkie są osiągane w tej samej konfiguracji urządzenia); prędkość = 1 MHz cykle odczytu-zapisu, liczba stanów > 50 (przestrajalny), zakres rezystancji = 50-100 nS (przestrajalny), wytrzymałość >10 8 operacji zapisu, rozmiar = 50×50 μm 2 .

Badania IBM

Jak donosi Seyoung Kim, John Rozen i in. od IBM Research:

Wykorzystując komórki ECRAM z tlenkiem metali, bez selektorów, zespół demonstruje równoległe programowanie i adresowanie w macierzach 2×2. W szczególności, zadanie regresji logistycznej jest wykonywane w pamięci z użyciem 1000 wektorów 2×1 jako zbioru uczącego. Dopasowanie krzywej 2D osiąga się w kilkunastu epokach.

Poszczególne komórki mają następujące właściwości (nie wszystkie są osiągane w tej samej konfiguracji urządzenia); prędkość = 10 ns zapis impulsów, liczba stanów > 1000 (przestrajalny), zakres rezystancji = 0-50 μS (przestrajalny), wytrzymałość >10 7 operacji zapisu, rozmiar < 1×1 μm 2 .

Implementacje komórek

Różne instytucje zademonstrowały komórki ECRAM z bardzo różnymi materiałami, układami i osiągami.

Przykładowy zestaw komórek dyskretnych znajduje się w tabeli.

| Jon | Kanał | Rozmiar urządzenia | Wpisz długość impulsu | Odniesienie |

|---|---|---|---|---|

| Li+ |

WO 3 |

100x 100 nm 2 | 5 ns | |

| Li+ |

Li 1−xWSPÓŁ 2 |

~1 mm 2 | 0,5 sekundy | |

| Li+ |

Grafen | 36 μm 2 | 10 ms | |

| Li+ |

α-MO 3 |

~1 mm 2 | 10 ms | |

| h+ |

PEDOT: PSS | 0,001 mm 2 | 5 ms | |

| h+ |

WO 3 |

0,05 mm 2 | 5 ms | |

| h+ |

WO 3 |

0,025 mm 2 | 210 ms | |

| h+ |

WO 3 |

0,01 mm 2 | 0,1 sekundy |

Li-ECRAM

Oparte na jonach litu urządzenia Li-ECRAM wykazały powtarzalne i kontrolowane przełączanie poprzez zastosowanie znanych materiałów z technologii baterii do konstrukcji pamięci. W konsekwencji takie komórki mogą wykazywać OCP, które zmienia się w ciągu kilku woltów, w zależności od zaprogramowanego stanu.

H-ECRAM

Oparte na jonach wodorowych urządzenia H-ECRAM okazały się szybkie, co wymaga niewielkich sił napędowych do wywołania programowania. Wysokim współczynnikom dyfuzji w różnych materiałach może towarzyszyć brak retencji w komórce pamięci, wpływając na wytrzymałość. Większość projektów H-ECRAM wykorzystuje elektrolity płynne i/lub organiczne.

MO-ECRAM

ECRAM oparte na tlenkach metali, są inspirowane materiałami OxRam i technologią bramek o wysokim współczynniku k/metal , stosowaną w komercyjnych ofertach półprzewodników. MO-ECRAM umożliwia pomijalne operacje zapisu OCP i sub-μs.

VLSI

W przypadku zaawansowanych aplikacji pamięci półprzewodnikowych lub obliczeniowych technologia musi być zgodna z integracją o bardzo dużej skali (VLSI) . Nakłada to ograniczenia na stosowane materiały i techniki stosowane do wytwarzania funkcjonalnych urządzeń. Konsekwencje dla ECRAM są opisane tutaj.

Odlewnia półprzewodników

Półprzewodników odlewni może obsługiwać kilka technologii i ma ścisłych reguł, jeśli chodzi o materiały wprowadzane w jego drogiego zestawu narzędzi w celu uniknięcia zanieczyszczenia krzyżowego i utratę wydajności urządzenia. W szczególności ruchome jony metali, jeśli są obecne w obszarach aktywnych, mogą indukować dryf urządzenia i wpływać na niezawodność. Istnieje kilka innych kwestii dotyczących odlewni; w tym bezpieczeństwo, koszt, objętość itp. W związku z tym Li-ECRAM na bazie litowo-jonowej staje przed wyjątkowymi wyzwaniami, poza obecnością OCP.

Tylny koniec linii (BEOL)

Macierze pamięci wymagają peryferii logicznych do działania i łączenia się z resztą systemu obliczeniowego. Takie peryferia oparte są na tranzystorach polowych (FET) zbudowanych na powierzchni podłoży płytek krzemowych o wysokim budżecie termicznym na początku linii (FEOL) . Komórki pamięci można umieszczać między górnymi metalowymi poziomami na końcu linii (BEOL), ale nadal nie mają na nie wpływu temperatury do ~400 °C stosowane w kolejnych krokach. Wraz z wyzwaniami związanymi z tworzeniem wzorów o wysokiej gęstości, ograniczenia te sprawiają, że urządzenia organiczne nie nadają się do takiej integracji.

Integracja heterogeniczna (HI)

Jednym ze sposobów wprowadzenia nowatorskich materiałów do pamięci może być zastosowanie heterogenicznej integracji (HI), w której macierz urządzeń jest wytwarzana niezależnie od elementów sterujących logicznych, a następnie połączona z chipem zawierającym FET, aby umożliwić jej wykorzystanie jako pamięci o dużej przepustowości (HBM) . Jednak koszt i złożoność związane z takim schematem negatywnie wpływają na propozycję wartości dla zastąpienia istniejących technologii pamięci.

Bibliografia

Linki zewnętrzne

- Moore, SK (11 grudnia 2018 r.). „Poszukiwanie idealnej sztucznej synapsy dla sztucznej inteligencji” . Widmo IEEE .

- Ambrogio, S.; Adusumilli, P.; Eleftheriou, E. (11 grudnia 2019 r.). „Droga do „doskonałego” analogowego materiału i systemu: IBM w IEDM i NeurIPS” . Blog badawczy IBM .

- Chandler, DL (19 czerwca 2020). „Inżynierowie projektują urządzenie, które działa jak synapsa mózgu” . Aktualności MIT .

- Kubota, T. (25 kwietnia 2019). „Sztuczna synapsa naukowców ze Stanford jest szybka, wydajna i trwała” . Aktualności Stanforda .

- „Sandia Powers przełomy w obliczeniach neuromorficznych” . wewnątrz HPC . 1 maja 2019 r.