Procesory architektury MIPS - MIPS architecture processors

Od 1985 roku wiele procesorów implementujących niektóre wersje architektury MIPS zostało zaprojektowanych i szeroko stosowanych.

Mikroprocesory MIPS

Pierwszy mikroprocesor MIPS, R2000 , został ogłoszony w 1985 roku. Dodał on instrukcje wielokrotnego mnożenia i dzielenia w nieco niezależnej jednostce na chipie. Dodano nowe instrukcje, aby pobrać wyniki z tej jednostki z powrotem do pliku rejestru procesora ; te instrukcje wyszukiwania wyników były ze sobą powiązane.

R2000 można było uruchomić z big-endian lub little-endian . Miał trzydzieści jeden 32-bitowych rejestrów ogólnego przeznaczenia, ale nie miał rejestru statusu ( rejestr kodu stanu (CCR), projektanci uznali go za potencjalne wąskie gardło), cechę wspólną z AMD 29000 , DEC Alpha i RISC-V . W przeciwieństwie do innych rejestrów licznik programu nie jest bezpośrednio dostępny.

R2000 miał również obsługę do czterech koprocesorów, z których jeden był wbudowany w główną jednostkę centralną (CPU) i obsługiwał wyjątki, pułapki i zarządzanie pamięcią, podczas gdy pozostałe trzy pozostawiono do innych zastosowań. Jeden z nich może być wypełniony przez opcjonalną jednostkę zmiennoprzecinkową (FPU) R2010 , która ma trzydzieści dwa 32-bitowe rejestry, które mogą być używane jako szesnaście rejestrów 64-bitowych dla podwójnej precyzji.

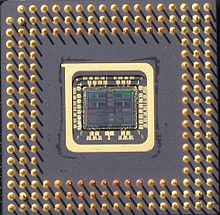

R3000 zastąpił R2000 w 1988 roku, dodając 32 KB (wkrótce podniesiony do 64 kb) pamięć podręczna dla instrukcji i danych oraz wsparcie dla pamięci współdzielonej- wieloprocesorowe w postaci spójności pamięci podręcznej protokołu. Chociaż w obsłudze procesorów wieloprocesorowych R3000 występowały wady, z powodzeniem zastosowano je w kilku udanych komputerach wieloprocesorowych. R3000 zawierał również wbudowaną jednostkę zarządzania pamięcią (MMU), wspólną cechę procesorów tej epoki. R3000, podobnie jak R2000, może być sparowany z FPU R3010 . R3000 był pierwszym udanym projektem MIPS na rynku i ostatecznie wyprodukowano ponad milion. Szybsza wersja R3000 działająca do 40 MHz, R3000A zapewniała wydajność 32 milionów instrukcji na sekundę (MIPS) lub jednostkę wydajności VAX (VUP). MIPS R3000A -Kompatybilny R3051 działa na 33.8688 MHz to procesor używany w Sony PlayStation choć nie mają FPU lub MMU. Projekty stron trzecich obejmują przeprowadzanie Semiconductor R3400 i IDT na R3500 , obaj byli R3000As ze zintegrowanym R3010 FPU. Toshiba „s R3900 był praktycznie pierwszy system-on-a-chip (SoC) do wczesnego przenośnych komputerów , które biegły Windows CE . Radiacyjnie utwardzony wariant zewnętrznego stosowania przestrzeni kosmicznej Mongoose-V , to R3000 ze zintegrowanym R3010 FPU.

Seria R4000 , wydana w 1991 roku, rozszerzyła MIPS do pełnego 64-bitowego projektu Word , przeniosła FPU na główną matrycę, tworząc mikroprocesor jednoukładowy, i miała wtedy wysoką częstotliwość taktowania 100 MHz na początku. Jednak, aby osiągnąć częstotliwość zegara, pamięć podręczna została zmniejszona do 8 KB każda, a dostęp do nich zajęło trzy cykle. Wysokie częstotliwości taktowania osiągnięto dzięki metodzie głębokiego pipeliningu (zwanej wówczas superpipeliningiem ). Ulepszony R4400 pojawił się w 1993 roku. Miał większą podstawową pamięć podręczną 16 KB, w dużej mierze wolne od błędów działanie 64-bitowe i obsługę większej pamięci podręcznej L2.

MIPS, obecnie oddział Silicon Graphics (SGI) o nazwie MTI, zaprojektował tani R4200 , podstawę dla jeszcze tańszego R4300i . Pochodna tego mikroprocesora, NEC VR4300, została zastosowana w konsoli do gier Nintendo 64 .

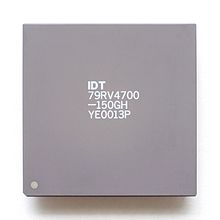

Efekt Quantum Devices (QED), oddzielna firma rozpoczęła byłego MIPS pracowników, mających na R4600 Orion , z R4700 Orion , z R4650 i R5000 . Tam, gdzie R4000 przyspieszył częstotliwość zegara i poświęcił pojemność pamięci podręcznej, projekty QED kładły nacisk na duże pamięci podręczne, do których można było uzyskać dostęp w zaledwie dwóch cyklach i wydajne wykorzystanie powierzchni krzemowej. R4600 i R4700 były używane w tanich wersjach stacji roboczej SGI Indy, a także w pierwszych routerach Cisco opartych na MIPS, takich jak routery z serii 36x0 i 7x00. R4650 użyto w oryginalnym WebTV dekoderów (obecnie Microsoft telewizora). R5000 FPU miały bardziej elastyczne pojedynczej precyzji zmiennoprzecinkową harmonogramu niż R4000, iw rezultacie, R5000 oparte SGI Indys miał znacznie lepszą wydajność grafiki niż podobnie taktowany R4400 Indys z tej samej karty graficznej. SGI nadało starej karcie graficznej nową nazwę po połączeniu z R5000 , aby podkreślić poprawę. Firma QED zaprojektowała później rodzinę urządzeń RM7000 i RM9000 dla rynków systemów wbudowanych, takich jak sieci komputerowe i drukarki laserowe. QED została przejęta przez producenta półprzewodników PMC-Sierra w sierpniu 2000 roku, ta ostatnia firma nadal inwestuje w architekturę MIPS. RM7000 zawiera zintegrowany 256 KB pamięci podręcznej L2 oraz kontroler pamięci podręcznej L3 dla opcjonalnego. RM9xx0 były rodzina SOC urządzeń, które zawarte Northbridge urządzeń peryferyjnych, takich jak kontroler pamięci , PCI kontrolera, Gigabit Ethernet kontroler i szybkiego I / O, takie jak HyperTransport portu.

R8000 (1994) był pierwszym Superskalarna projekt MIPS, w stanie wykonać dwa całkowitą lub zmiennoprzecinkowych oraz dwie instrukcje pamięci w jednym cyklu. Projekt został rozłożony na sześć układów: jednostkę integer (z instrukcjami 16 KB i pamięcią podręczną danych 16 KB), jednostkę zmiennoprzecinkową, trzy w pełni niestandardowe pamięci RAM z tagami dodatkowej pamięci podręcznej (dwie dla dostępu do drugorzędnej pamięci podręcznej, jeden do podsłuchiwania magistrali), i kontroler pamięci podręcznej ASIC. Projekt miał dwie w pełni potokowe jednostki podwójnej precyzji dodawania, które mogły przesyłać strumieniowo dane z 4 MB dodatkowej pamięci podręcznej poza układem. R8000 zasilał serwery SGI POWER Challenge w połowie lat 90., a później stał się dostępny w stacji roboczej POWER Indigo2. Chociaż jego wydajność FPU całkiem dobrze pasuje do użytkowników naukowych, jego ograniczona wydajność w liczbach całkowitych i wysokie koszty osłabiają atrakcyjność dla większości użytkowników. R8000 był sprzedawany tylko przez rok i pozostaje dość rzadki.

W 1995 roku wypuszczono R10000 . Ten procesor był konstrukcją jednoukładową, działał z wyższą częstotliwością zegara niż R8000 i miał większe 32 KB podstawowe instrukcje i pamięć podręczną danych. Był również superskalarny, ale jego główną innowacją było wykonanie poza kolejnością . Nawet przy jednym potoku pamięci i prostszym FPU, znacznie lepsza wydajność w liczbach całkowitych, niższa cena i wyższa gęstość sprawiły, że R10000 jest preferowany przez większość klientów.

Niektóre późniejsze projekty były oparte na rdzeniu R10000. W R12000 zastosowano proces 0,25 mikrometra, aby zmniejszyć chip i osiągnąć wyższe częstotliwości taktowania . Zmieniony R14000 umożliwił wyższe częstotliwości taktowania z dodaną obsługą synchronicznej dynamicznej pamięci o dostępie swobodnym ( DDR SDRAM ) statycznej pamięci o dostępie swobodnym (SRAM) o podwójnej szybkości przesyłania danych w pamięci podręcznej poza układem . Późniejsze iteracje noszą nazwy R16000 i R16000A i charakteryzują się wyższymi częstotliwościami taktowania oraz mniejszą produkcją matryc w porównaniu z poprzednimi.

Inni członkowie rodziny MIPS obejmują R6000 , implementację logiki sprzężonej z emiterem (ECL) wyprodukowaną przez Bipolar Integrated Technology . R6000 wprowadził architekturę MIPS II. Jego bufor translacji (TLB) i architektura pamięci podręcznej różnią się od wszystkich innych członków rodziny MIPS. Model R6000 nie zapewnił obiecanych korzyści w zakresie wydajności i chociaż znalazł pewne zastosowanie w maszynach Control Data , szybko zniknął z głównego nurtu rynku.

Historia

Pierwszy sprzęt

W 1981 r. John L. Hennessy rozpoczął na Uniwersytecie Stanforda projekt MIPS ( Microprocessor without Interlocked Pipeline Stages ) w celu zbadania technologii komputerów o zredukowanych zestawach instrukcji (RISC). Wyniki jego badań przekonały go o przyszłym komercyjnym potencjale technologii i w 1984 roku wziął urlop, aby założyć MIPS Computer Systems . Firma zaprojektowała nową architekturę, która również została nazwana MIPS , i wprowadziła pierwszą implementację MIPS, R2000 , w 1985 roku. R2000 został ulepszony, a projekt został wprowadzony jako R3000 w 1988 roku. Te 32-bitowe procesory stanowiły podstawę ich firma w latach 80. była używana głównie w stacjach roboczych Silicon Graphics (SGI), a później stacjach roboczych i serwerach Digital Equipment Corporation DECstation. Komercyjne projekty SGI odbiegały od Stanford MIPS, implementując większość blokad w sprzęcie, dostarczając pełne instrukcje mnożenia i dzielenia (m.in.). Projekty były częściowo kierowane przez architekta oprogramowania Earla Killiana, który zaprojektował rozszerzenie 64-bitowego zestawu instrukcji MIPS III i kierował pracami nad mikroarchitekturą R4000.

W 1991 roku ukazała się pierwsza MIPS 64-bitowy mikroprocesor , na R4000 . MIPS miał jednak trudności finansowe przy wprowadzaniu go na rynek. Projekt był tak ważny dla SGI, wówczas jednego z nielicznych głównych klientów MIPS, że SGI kupiło firmę w 1992 roku, aby zagwarantować, że projekt nie zostanie utracony. Nowa filia SGI została nazwana MIPS Technologies .

Architektura podlegająca licencjonowaniu

Na początku lat 90. MIPS zaczął udzielać licencji na swoje projekty zewnętrznym dostawcom. Okazało się to dość udane ze względu na prostotę rdzenia, co pozwoliło na wiele zastosowań, które wcześniej wykorzystywały znacznie mniej wydajne konstrukcje komputerów z zestawem instrukcji (CISC) o podobnej liczbie bramek i cenie; obie są ściśle powiązane: cena procesora jest generalnie związana z liczbą bramek i liczbą zewnętrznych pinów. Sun Microsystems próbował odnieść podobny sukces, licencjonując swój rdzeń SPARC, ale nie odniósł takiego sukcesu. Pod koniec lat 90. MIPS był potęgą w dziedzinie procesorów wbudowanych . Według MIPS Technologies Inc. nastąpił gwałtowny wzrost, z 48-milionowymi dostawami procesorów opartych na MIPS i 49% całkowitego udziału w rynku procesorów RISC w 1997 roku. MIPS odniósł tak wielki sukces, że SGI wydzieliła MIPS Technologies w 1998 roku. połowa dochodów MIPS pochodziła z licencjonowania ich projektów, podczas gdy znaczna część pochodziła z kontraktowych prac projektowych dotyczących rdzeni dla stron trzecich.

W 1999 roku firma MIPS Technologies zastąpiła poprzednie wersje architektury MIPS dwiema architekturami, 32-bitową MIPS32 (opartą na MIPS II z kilkoma dodanymi funkcjami MIPS III, MIPS IV i MIPS V) oraz 64-bitową MIPS64 (opartą na na MIPS V) do licencjonowania. Nippon Electric Corporation ( NEC ), Toshiba i SiByte (później przejęte przez Broadcom ) otrzymały licencje na MIPS64, gdy tylko zostało to ogłoszone. Od tego czasu dołączyły do nich firmy Philips , LSI Logic i Integrated Device Technology (IDT). Dziś rdzenie MIPS są jednymi z najczęściej używanych rdzeni „ciężkich” na rynku urządzeń podobnych do komputerów: komputerów przenośnych , dekoderów itp.

Ponieważ architektura MIPS jest licencjonowana, na przestrzeni lat przyciągnęła ona kilka firm rozpoczynających działalność w zakresie procesorów . Jednym z pierwszych start-upów zajmujących się projektowaniem procesorów MIPS było Quantum Effect Devices (patrz następny rozdział). Zespół projektowy MIPS, który zaprojektował R4300i, założył firmę SandCraft , która zaprojektowała R5432 dla NEC, a później wyprodukowała SR71000 , jeden z pierwszych procesorów wykonawczych poza kolejnością dla rynku urządzeń wbudowanych. Oryginalny zespół DEC StrongARM ostatecznie podzielił się na dwa start-upy oparte na MIPS: SiByte, który wyprodukował SB-1250 , jeden z pierwszych wysokowydajnych systemów opartych na MIPS (SOC); podczas gdy Alchemy Semiconductor (później przejęty przez AMD ) wyprodukował Au-1000 SoC do zastosowań o niskim poborze mocy. Lexra zastosowała architekturę podobną do MIPS i dodała rozszerzenia DSP dla rynku chipów audio oraz obsługę wielowątkowości dla rynku sieciowego. Ponieważ Lexra nie licencjonowała architektury, między obiema firmami wszczęto dwa procesy sądowe. Pierwszy został szybko rozwiązany, gdy Lexra obiecała, że nie będzie reklamować swoich procesorów jako zgodnych z MIPS. Druga (dotycząca patentu MIPS 4814976 do obsługi niewyrównanego dostępu do pamięci) była przedłużana, zaszkodziła biznesowi obu firm i zakończyła się przyznaniem Lexrze przez MIPS Technologies darmowej licencji i dużej gotówki.

Pojawiły się dwie firmy specjalizujące się w budowie urządzeń z procesorami wielordzeniowymi z wykorzystaniem architektury MIPS. Raza Microelectronics, Inc. kupiła linię produktów od upadającego SandCrafta, a później wyprodukowała urządzenia zawierające osiem rdzeni dla rynków telekomunikacyjnych i sieciowych. Cavium , pierwotnie producent procesorów bezpieczeństwa, produkował również urządzenia z ośmioma rdzeniami procesora, a później do 32 rdzeni, na te same rynki. Obie te firmy zaprojektowały swoje rdzenie we własnym zakresie, licencjonując tylko architekturę, zamiast kupować rdzenie od MIPS.

Pulpit

Wśród producentów, którzy stworzyli komputerowe systemy stacji roboczych z procesorami MIPS są SGI , MIPS Computer Systems, Inc. , Whitechapel Workstations , Olivetti , Siemens-Nixdorf , Acer , Digital Equipment Corporation , NEC i DeskStation .

Systemy operacyjne przeniesiony do architektury obejmują SGI IRIX , Microsoft 's Windows NT (poprzez v4.0), Windows CE , Linux , FreeBSD , NetBSD , OpenBSD , UNIX System V , SINIX , QNX oraz MIPS Computer Systems' własne RISC / os .

Na początku lat 90. pojawiły się spekulacje, że MIPS i inne potężne procesory RISC prześcigną architekturę Intel IA-32 . Ten został zachęcony przez wsparciu pierwszych dwóch wersjach Microsoft „s Windows NT dla Alpha , MIPS i PowerPC , oraz w mniejszym stopniu architekturę Clipper i SPARC . Jednak, gdy Intel szybko wypuścił szybsze wersje swoich procesorów klasy Pentium , Microsoft Windows NT v4.0 zrezygnował z obsługi czegokolwiek poza IA-32 i Alpha. Wraz z decyzją SGI o przejściu na architektury Itanium i IA-32 w 2007 r. (po bankructwie w 2006 r. w rozdziale 11) i przejęciu w 2009 r. przez Rackable Systems, Inc. wsparcie dla rynku konsumenckiego MIPS/IRIX zakończyło się w grudniu 2013 r., jak pierwotnie zaplanowany. Jednak zespół wsparcia nadal istnieje dla szczególnych okoliczności i odnowionych systemów, które są nadal dostępne w ograniczonym zakresie.

Rynki wbudowane

Przez 1990, architektura MIPS została szeroko przyjęta przez osadzonego rynku, w tym do stosowania w sieciach komputerowych , telekomunikacji , gier arcade wideo , konsole do gier wideo , drukarek komputerowych , cyfrowych dekoderów , telewizorów cyfrowych , DSL i modemy kablowe i osobiści asystenci cyfrowi .

Niski pobór mocy i charakterystyka cieplna wbudowanych implementacji MIPS, szeroka dostępność wbudowanych narzędzi programistycznych oraz wiedza na temat architektury oznaczają, że użycie mikroprocesorów MIPS we wbudowanych rolach prawdopodobnie pozostanie powszechne.

Syntezowalne rdzenie dla rynków wbudowanych

W ostatnich latach większość technologii stosowanych w różnych generacjach MIPS była oferowana jako półprzewodnikowe rdzenie własności intelektualnej (rdzenie IP), jako bloki konstrukcyjne dla wbudowanych procesorów . Oferowane są zarówno 32-bitowe, jak i 64-bitowe rdzenie podstawowe, znane jako 4K i 5K . Rdzenie te można mieszać z dodatkowymi jednostkami, takimi jak jednostki zmiennoprzecinkowe (FPU), systemy z pojedynczą instrukcją, wieloma danymi ( SIMD ), różne urządzenia wejścia/wyjścia (I/O) itp.

Rdzenie MIPS odniosły sukces komercyjny, mając obecnie wiele zastosowań konsumenckich i przemysłowych. Rdzenie MIPS można znaleźć w nowszych routerach Cisco , Linksys i Mikrotik, modemach kablowych i modemach z asymetryczną cyfrową linią abonencką (ADSL), kartach inteligentnych , silnikach drukarek laserowych , dekoderach , robotach i komputerach podręcznych. W telefonach komórkowych i PDA MIPS w dużej mierze nie był w stanie zastąpić dotychczasowej, konkurencyjnej architektury ARM .

Procesory architektury MIPS obejmują: IDT RC32438; ATI/AMD Xilleon ; Alchemia Au1000, 1100, 1200; Wartownik Broadcom5; RMI XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx i CN5xxx; Infineon Technologies EasyPort, Amazon, Dunaj, ADM5120, WildPass, INCA-IP, INCA-IP2; Technologia mikroprocesorowa PIC32; NEC EMMA i EMMA2, NEC VR4181A, VR4121, VR4122, VR4181A, VR4300, VR5432, VR5500; Generacja technologii dębowych ; PMC-Sierra RM11200; QuickLogic QuickMIPS ESP; Toshiba Donau , Toshiba TMPR492x, TX4925, TX9956, TX7901; KOMDIV-32 , KOMDIV-64 , ELVEES Multicore z Rosji.

Superkomputery oparte na MIPS

Jednym z interesujących, mniej powszechnych zastosowań architektury MIPS są superkomputery z ogromną liczbą procesorów. Silicon Graphics (SGI) na początku lat 90. przestawiło swoją działalność z desktopowych stacji graficznych na rynek obliczeń o wysokiej wydajności . Sukces pierwszego wejścia firmy w systemy serwerowe, serii Challenge opartej na R4400 i R8000 , a później R10000 , zmotywował SGI do stworzenia znacznie potężniejszego systemu. Wprowadzenie zintegrowanego R10000 pozwoliło SGI wyprodukować system Origin 2000 , ostatecznie skalowalny do 1024 procesorów przy użyciu połączenia NUMAlink cc-NUMA. Origin 2000 zapoczątkował serię Origin 3000, która osiągnęła szczyt z taką samą maksymalną liczbą procesorów 1024, ale używając chipów R14000 i R16000 do 700 MHz. Jego superkomputery oparte na MIPS zostały wycofane w 2005 roku, kiedy SGI podjęła strategiczną decyzję o przejściu na architekturę Intel Itanium IA-64 .

Firma SiCortex, start- up zajmujący się obliczeniami o wysokiej wydajności, wprowadził w 2007 r. masowo równoległy superkomputer oparty na MIPS. Maszyny są oparte na architekturze MIPS64 i połączeniu o wysokiej wydajności wykorzystującym topologię grafu Kautza . System jest bardzo wydajny energetycznie i mocny obliczeniowo. Najbardziej innowacyjnym aspektem systemu był jego wielordzeniowy węzeł przetwarzania, który integruje sześć rdzeni MIPS64, kontroler pamięci przełącznika krzyżowego , silnik bezpośredniego dostępu do pamięci (DMA), kontrolery Gigabit Ethernet i PCI Express, a wszystko to w jednym układzie, który zużywa tylko 10 watów moc, ale ma szczytową wydajność zmiennoprzecinkową 6 giga FLOPS . Najpotężniejsza konfiguracja, SC5832, to superkomputer z pojedynczą szafą, składający się z 972 takich chipów węzłów, co daje łącznie 5832 rdzeni procesorów MIPS64 i 8,2 teraFLOPS o szczytowej wydajności.

Loongson

Loongson to rodzina zgodnych z MIPS mikroprocesorów zaprojektowanych przez Instytut Technologii Komputerowych (ICT) Chińskiej Akademii Nauk . Wczesne modele, niezależnie zaprojektowane przez Chińczyków, nie miały obsługi czterech instrukcji, które zostały opatentowane przez MIPS Technologies. W czerwcu 2009 r. ICT udzieliła licencji MIPS Technologies na architekturę MIPS32 i MIPS64. Począwszy od 2006 roku, wiele firm wypuszczało komputery oparte na Loongson, w tym nettopy i netbooki zaprojektowane z myślą o niskim zużyciu energii.

W ostatnich latach dedykowany układ Loongson (1E04/1E0300/1E1000,1F04/1F0300,1J) był używany na 3–5 satelitach nawigacyjnych Beidou.

Świt 6000

Superkomputer Dawning 6000 , który ma przewidywaną wydajność ponad 1 P FLOPS , będzie korzystał z procesora Loongson . Dawning 6000 jest obecnie opracowywany wspólnie przez ICT i Dawning Information Industry Company. Li Guojie, prezes Dawning Information Industry Company oraz dyrektor i akademik ICT, powiedział, że badania i rozwój Dawning 6000 mają zostać zakończone w ciągu dwóch lat. Oczekuje się, że do tego czasu wysokowydajne komputery wyprodukowane w Chinach osiągną dwa główne cele: po pierwsze, wprowadzenie procesorów produkcji krajowej; po drugie, istniejąca struktura systemowa oparta na klastrach komputerów o wysokiej wydajności zostanie zmieniona, gdy wydajność osiągnie 1 PFLOPS.

MIPS Aptiv

Zapowiedziana w 2012 roku rodzina MIPS Aptiv obejmuje trzy 32-bitowe procesory oparte na architekturze MIPS32 Release 3.

microAptiv

microAptiv to kompaktowy, osadzony w czasie rzeczywistym rdzeń procesora z pięciostopniowym potokiem i zestawem instrukcji kompresji kodu microMIPS. microAptiv może być skonfigurowany jako mikroprocesor (microAptiv UP) z pamięcią podręczną instrukcji i danych oraz jednostką zarządzania pamięcią lub jako mikrokontroler (microAptiv UC) z jednostką ochrony pamięci (MPU). Jednostka centralna integruje funkcje DSP i SIMD, aby sprostać wymaganiom przetwarzania sygnału dla podstawowych segmentów wbudowanych, w tym sterowania przemysłowego, inteligentnych liczników, komunikacji samochodowej i przewodowej/bezprzewodowej.

interAptiv

interAptiv to wieloprocesorowy rdzeń wykorzystujący dziewięciostopniowy potok z wielowątkowością. Rdzeń może być używany do wysoce równoległych zadań wymagających optymalizacji kosztów i mocy, takich jak inteligentne bramy, przetwarzanie pasma podstawowego w sprzęcie użytkownika LTE i małych komórkach, kontrolery dysków półprzewodnikowych (SSD) i sprzęt motoryzacyjny.

proAptiv

proAptiv to superskalarny rdzeń procesora poza kolejnością, który jest dostępny w wersjach jedno- i wielordzeniowych. proAptiv jest przeznaczony do przetwarzania aplikacji w podłączonej elektronice użytkowej oraz przetwarzania płaszczyzny sterowania w sieci.

Wojownik MIPS

Zapowiedziana w czerwcu 2013 r. rodzina MIPS Warrior obejmuje wiele 32-bitowych i 64-bitowych procesorów opartych na architekturach MIPS Release 5 i 6.

Wojownik klasy M

32-bitowe rdzenie MIPS dla wbudowanych i mikrokontrolerów wykorzystuje:

- Rdzenie MIPS M5100 i MIPS M5150 (MIPS32 Release 5): pięciostopniowa architektura potokowa, microMIPS ISA, MIPS DSP Module r2, szybka obsługa przerwań, zaawansowane możliwości debugowania/profilowania i zarządzanie energią.

- Rdzenie MIPS M6200 i M6250 (MIPS32 Release 6): sześciostopniowa architektura potokowa, microMIPS ISA, dedykowany moduł DSP i SIMD

Wojownik I-klasa

64-bitowe procesory MIPS do wysokowydajnych, energooszczędnych zastosowań wbudowanych:

- Rdzeń wieloprocesorowy MIPS I6400 (MIPS64 Release 6): jednoczesna wielowątkowość (SMT), wirtualizacja sprzętowa, 128-bitowa karta SIMD, zaawansowane zarządzanie energią, wielokontekstowe zabezpieczenia, rozszerzalne do spójnego działania wieloklastrowego.

Wojownik klasy P

32-bitowe i 64-bitowe procesory aplikacji MIPS:

- Rdzeń wieloprocesorowy MIPS P5600 (MIPS32 wydanie 5): wirtualizacja sprzętowa z obsługą tabeli sprzętowej, 128-bitowa karta SIMD, 40-bitowa eXtended Physical Addressing (XPA)

- Rdzeń wieloprocesorowy MIPS P6600 (MIPS64 Release 6): wirtualizacja sprzętowa z obsługą tabeli sprzętowej, 128-bitowa karta SIMD